# SH7724

User's Manual: Hardware

Renesas 32-Bit RISC Microcomputer SH7780 Series

R8A7724

[Portions omitted in accordance with NDA]

The contents of the Video Processing Unit (VPU), 2D Graphic Accelerator (2DG), and Sound Process Unit 2 (SPU2) sections of this document are covered by a non-disclosure agreement. Please contact a Renesas Electronics sales representative for details.

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is

subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please

confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to

additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics

does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages

incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics sess incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this

document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## **General Precautions on Handling of Product**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are they are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

#### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

#### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

#### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

### 5. Reading from/Writing to Reserved Bit of Each Register

Note: Treat the reserved bit of register used in each module as follows except in cases where the specifications for values which are read from or written to the bit are provided in the description.

The bit is always read as 0. The write value should be 0 or one, which has been read immediately before writing.

Writing the value, which has been read immediately before writing has the advantage of preventing the bit from being affected on its extended function when the function is assigned.

# Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. Electrical Characteristics

- 8. Appendix

- 9. Index

## **Preface**

This LSI is a RISC (Reduced Instruction Set Computer) microcomputer which includes a Renesas original RISC CPU as its core, and the peripheral functions required to configure a system.

Target Users: This manual was written for users who will be using this LSI in the design of

application systems. Users of this manual are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

Objective: This manual was written to explain the hardware functions and electrical

characteristics of this LSI to the above users.

#### Notes on reading this manual:

In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts on the CPU, system control functions, peripheral functions and electrical characteristics.

In order to understand the details on FPU functions and each instructions

Read the additional volume, SH-4A Extended Functions Software Manual.

Rules: Bit order: The MSB is on the left and the LSB is on the right.

Number notation: Binary is B'xxxx, hexadecimal is H'xxxx, decimal is xxxx.

Signal notation: An overbar is added to a low-active signal:  $\overline{xxxx}$

#### **Abbreviations**

ATAPI ATAPI Controller

CPG Clock Pulse Generator

DMAC Direct Memory Access Controller

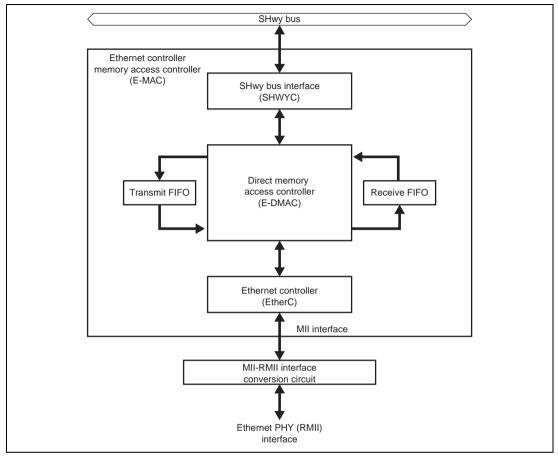

E-DMAC Ethernet Controller Direct Memory Access Controller

EtherC Ethernet Controller

FLCTL NAND Flash Memory Controller

G2D 2D Graphics Engine

GPIO General Purpose I/O

H-UDI User Debugging Interface

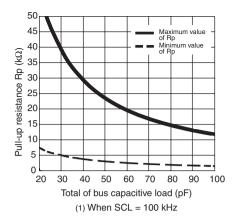

IIC I2C Bus Interface

INTC Interrupt Controller

MCU Memory Controller Unit

MMU Memory Management Unit

SCIF Serial Communication Interface with FIFO

TMU Timer Unit

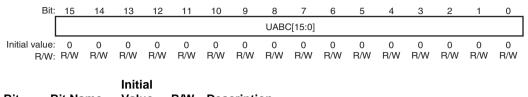

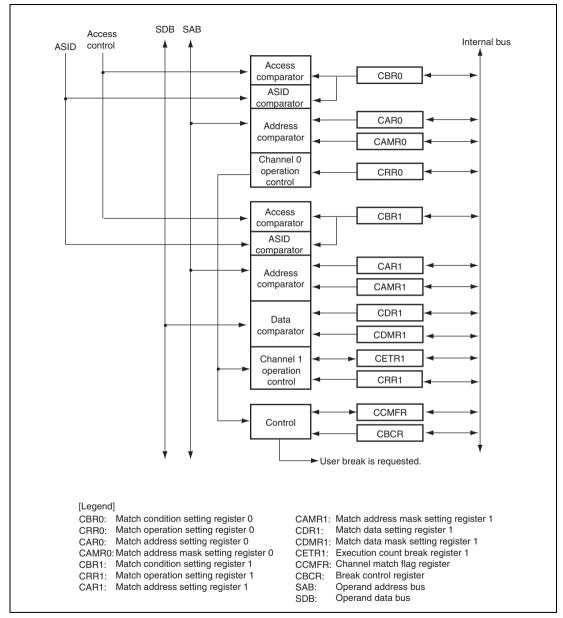

UBC User Break Controller

USB Host/Function Interface

VDC2 Video Display Controller 2

WDT Watchdog Timer and Reset

SSI Serial Sound Interface

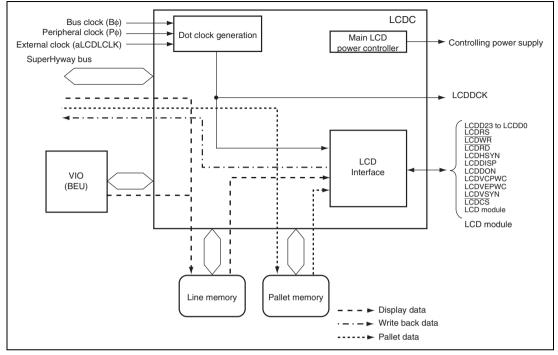

LCDC LCD Controller

SRC Sampling Rate Converter

bps bits per second

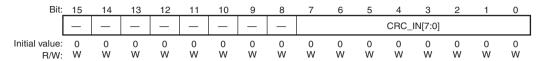

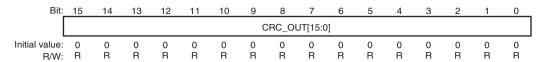

CRC Cyclic Redundancy Check

DMA Direct Memory Access

DMAC Direct Memory Access Controller

Hi-Z High Impedance

I/O Input/Output

LSB Least Significant Bit

MSB Most Significant Bit

NC Non-Connection

PLL Phase Locked Loop

All trademarks and registered trademarks are the property of their respective owners.

# Contents

| Secti | on 1 Overview                      | 1   |

|-------|------------------------------------|-----|

| 1.1   | SH7724 Features                    | 1   |

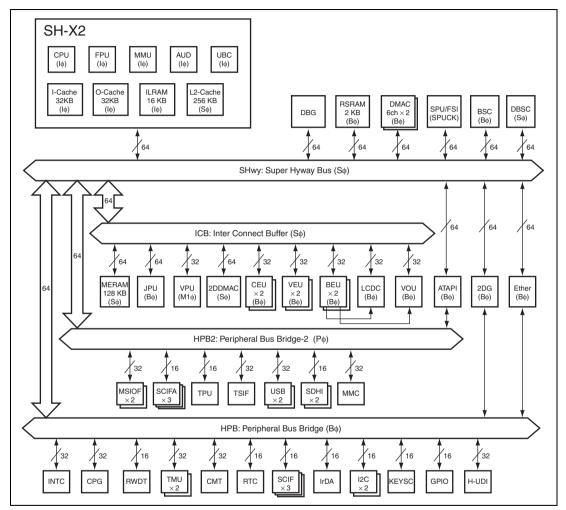

| 1.2   | Block Diagram                      | 3   |

| 1.3   | Overview of Module Specifications  | . 4 |

| 1.4   | Pin Assignment                     | 16  |

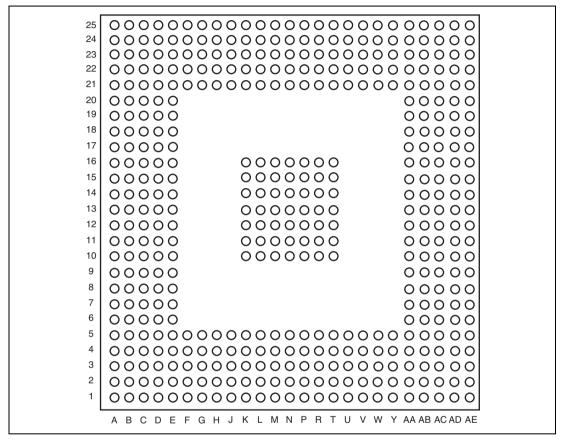

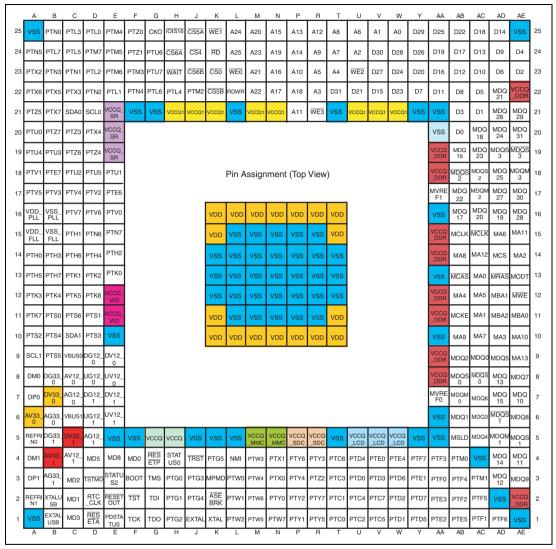

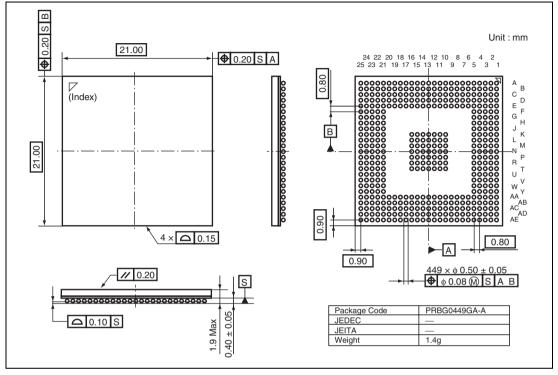

| 1.5   | Pin Assignment (BGA449)            | 18  |

| 1.6   | Pin Functions                      | 35  |

| 1.7   | Internal Bus Configuration.        | 45  |

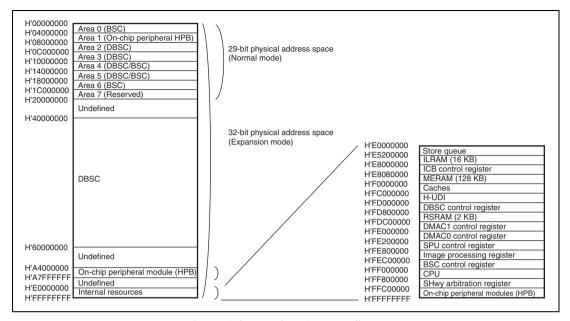

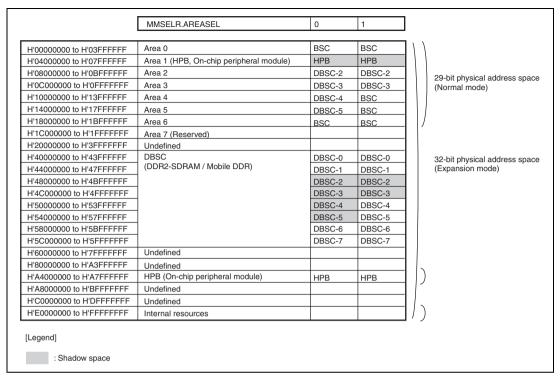

| 1.8   | Memory Address Map                 | 46  |

| 1.9   | Clocks                             |     |

| 1.10  | Operating Modes                    | 51  |

|       | 1.10.1 Reset                       |     |

|       | 1.10.2 Power-Down Modes            | 52  |

| 1.11  | Power Supply Sequence              | 53  |

| 1.12  | Notes on Board Design              | 54  |

|       |                                    |     |

|       | on 2 Programming Model             |     |

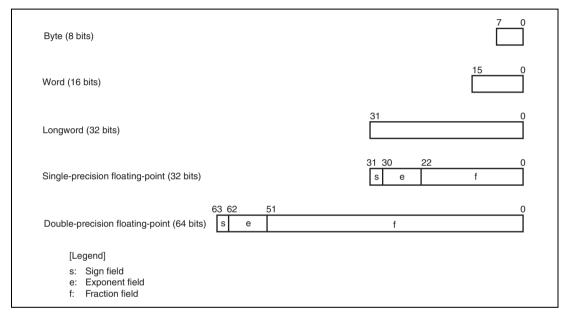

| 2.1   | Data Formats                       |     |

| 2.2   | Register Descriptions              |     |

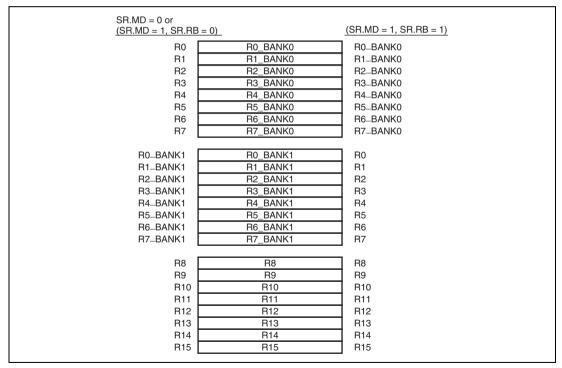

|       | 2.2.1 Privileged Mode and Banks    |     |

|       | 2.2.2 General Registers            |     |

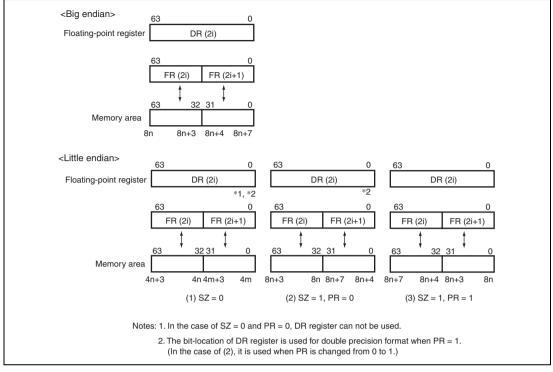

|       | 2.2.3 Floating-Point Registers     |     |

|       | 2.2.4 Control Registers            |     |

|       | 2.2.5 System Registers             |     |

| 2.3   | Memory-Mapped Registers            |     |

| 2.4   | Data Formats in Registers          |     |

| 2.5   | Data Formats in Memory             |     |

| 2.6   | Processing States                  |     |

| 2.7   | Usage Notes                        |     |

|       | 2.7.1 Notes on Self-Modifying Code | 73  |

| Secti | on 3 Instruction Set               | 75  |

| 3.1   | Execution Environment.             |     |

| 3.2   | Addressing Modes                   |     |

| 3 3   | Instruction Sat                    |     |

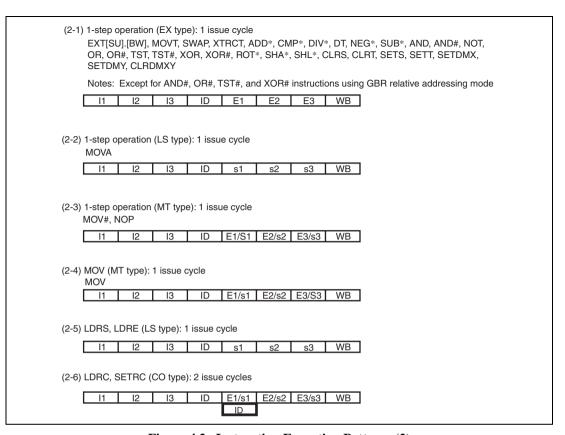

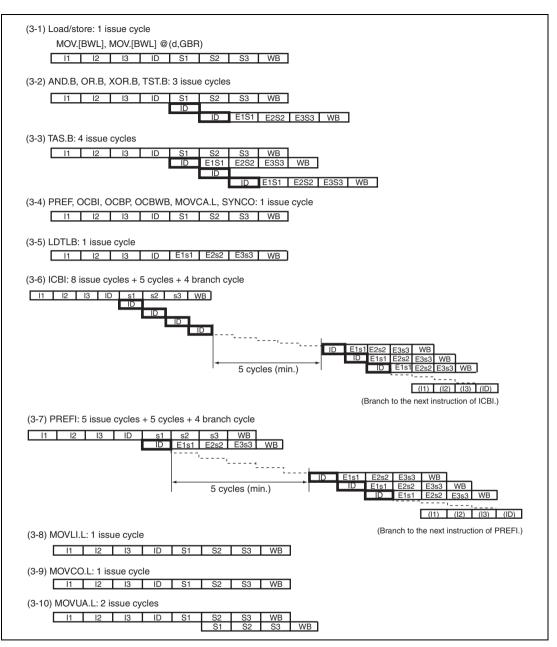

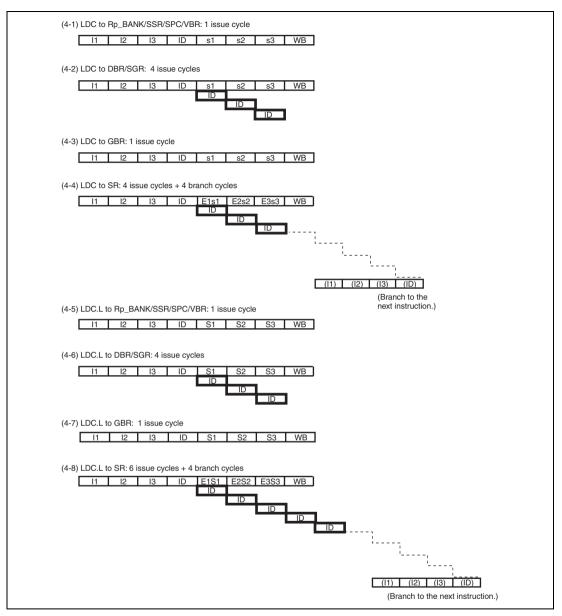

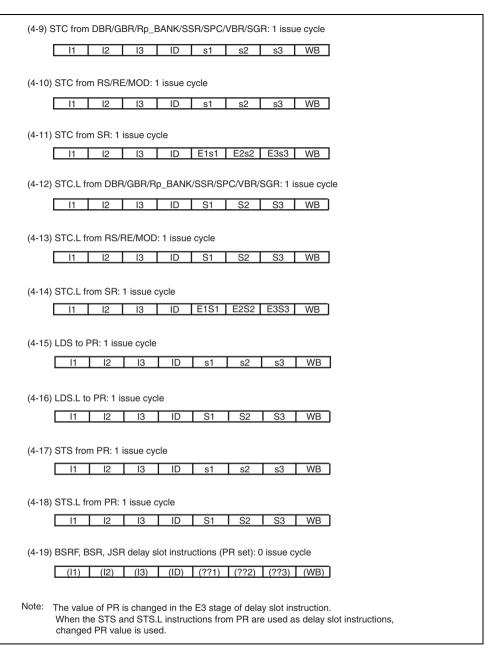

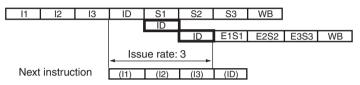

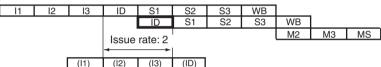

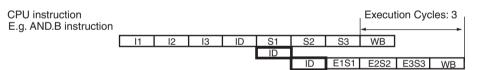

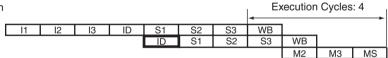

| Secti | ion 4   | Pipelining                                         | 95  |

|-------|---------|----------------------------------------------------|-----|

| 4.1   | Pipelin | ies                                                | 95  |

| 4.2   | Paralle | l-Executability                                    | 106 |

| 4.3   | Issue R | Rates and Execution Cycles                         | 109 |

| g     |         | P ' II 11'                                         | 110 |

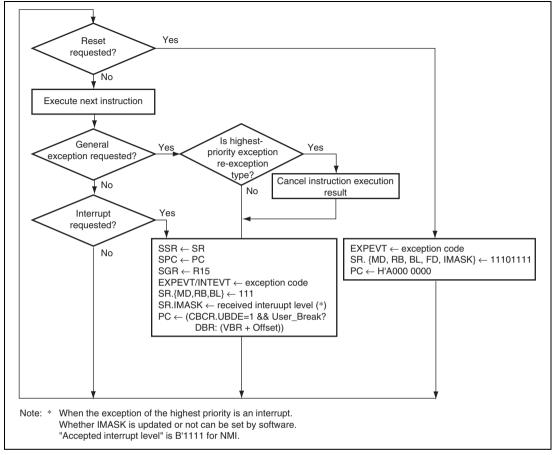

|       |         | Exception Handling                                 |     |

| 5.1   |         | ary of Exception Handling                          |     |

| 5.2   |         | er Descriptions                                    |     |

|       | 5.2.1   | TRAPA Exception Register (TRA)                     |     |

|       | 5.2.2   | Exception Event Register (EXPEVT)                  |     |

|       | 5.2.3   | Interrupt Event Register (INTEVT)                  |     |

|       | 5.2.4   | Non-Support Detection Exception Register (EXPMASK) |     |

| 5.3   | Except  | tion Handling Functions                            |     |

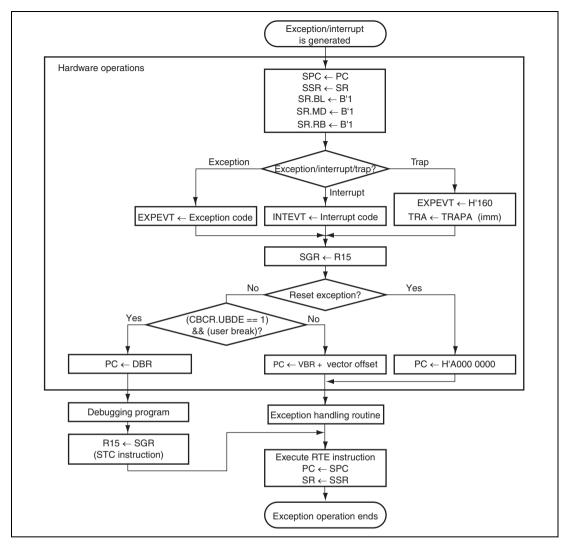

|       | 5.3.1   | Exception Handling Flow                            |     |

|       | 5.3.2   | Exception Handling Vector Addresses                | 125 |

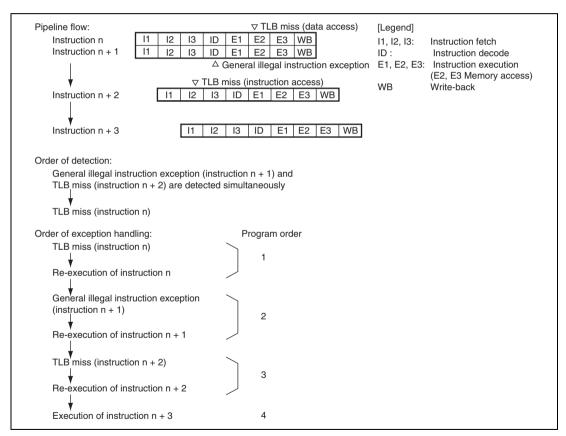

| 5.4   | Except  | tion Types and Priorities                          | 126 |

| 5.5   | Except  | tion Flow                                          | 128 |

|       | 5.5.1   | Exception Flow                                     | 128 |

|       | 5.5.2   | Exception Source Acceptance                        | 130 |

|       | 5.5.3   | Exception Requests and BL Bit                      | 131 |

|       | 5.5.4   | Return from Exception Handling                     | 131 |

| 5.6   | Descri  | ption of Exceptions                                | 132 |

|       | 5.6.1   | Resets                                             | 132 |

|       | 5.6.2   | General Exceptions                                 | 134 |

|       | 5.6.3   | Interrupts                                         |     |

|       | 5.6.4   | Priority Order with Multiple Exceptions            |     |

| 5.7   | Usage   | Notes                                              |     |

|       | C       |                                                    |     |

| Secti | ion 6   | Floating-Point Unit (FPU)                          | 155 |

| 6.1   | Feature | es                                                 | 155 |

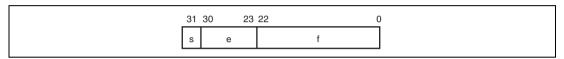

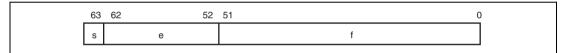

| 6.2   | Data F  | ormats                                             | 156 |

|       | 6.2.1   | Floating-Point Format                              | 156 |

|       | 6.2.2   | Non-Numbers (NaN)                                  | 159 |

|       | 6.2.3   | Denormalized Numbers                               | 160 |

| 6.3   | Registe | er Descriptions                                    |     |

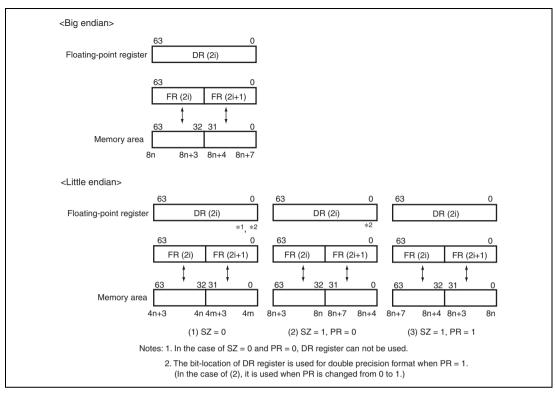

|       | 6.3.1   | Floating-Point Registers                           |     |

|       | 6.3.2   | Floating-Point Status/Control Register (FPSCR)     |     |

|       | 6.3.3   | Floating-Point Communication Register (FPUL)       |     |

| 6.4   |         | ing                                                |     |

| 6.5   |         | rg-Point Exceptions                                |     |

|       |         | ·                                                  |     |

|      | 6.5.1  | General FPU Disable Exceptions and Slot FPU Disable Exceptions |     |

|------|--------|----------------------------------------------------------------|-----|

|      | 6.5.2  | FPU Exception Sources                                          |     |

|      | 6.5.3  | FPU Exception Handling                                         |     |

| 6.6  | Graph  | ics Support Functions                                          |     |

|      | 6.6.1  | Geometric Operation Instructions                               |     |

|      | 6.6.2  | Pair Single-Precision Data Transfer                            | 172 |

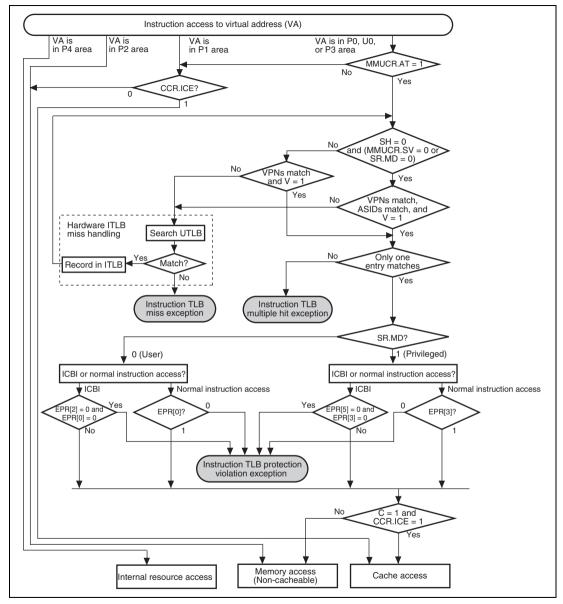

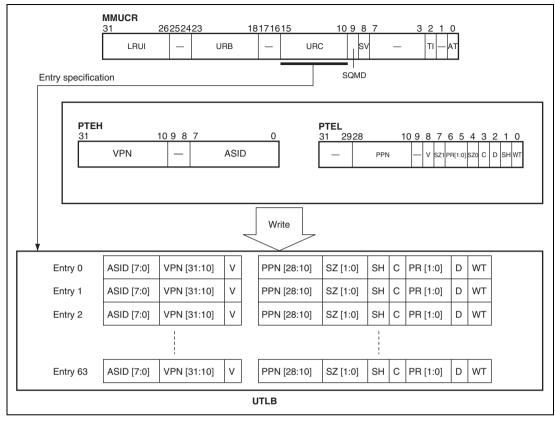

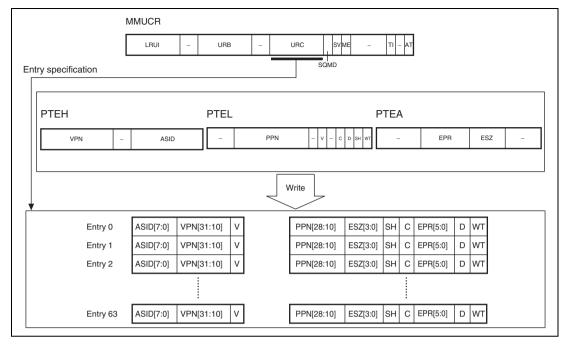

| Sect | ion 7  | Memory Management Unit (MMU)                                   | 173 |

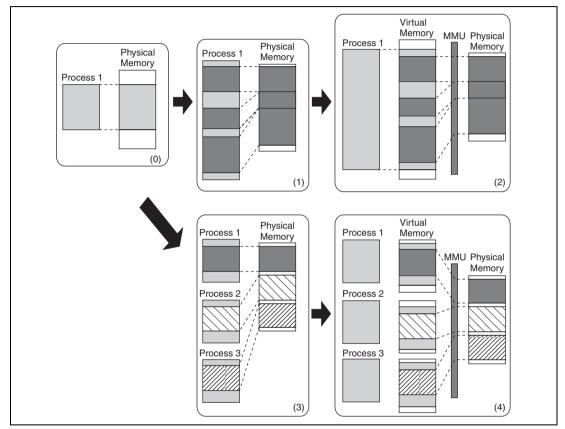

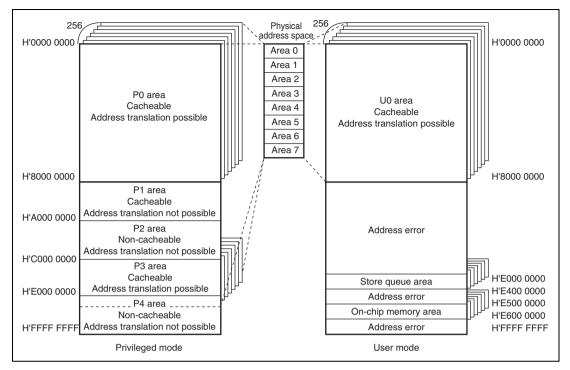

| 7.1  | Overv  | iew of MMU                                                     | 174 |

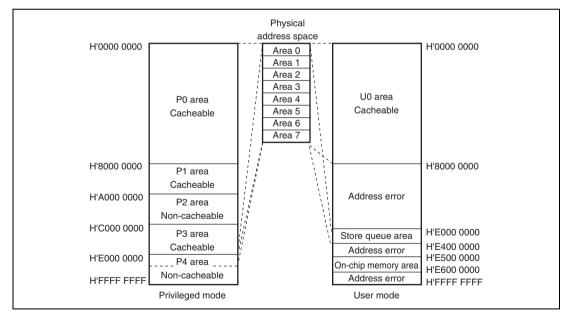

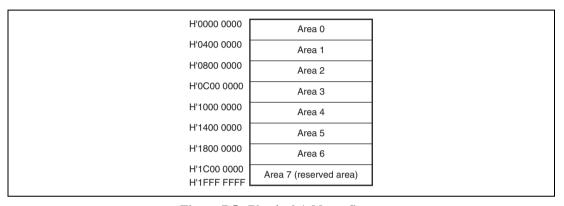

|      | 7.1.1  | Address Spaces                                                 | 176 |

| 7.2  | Regist | er Descriptions                                                |     |

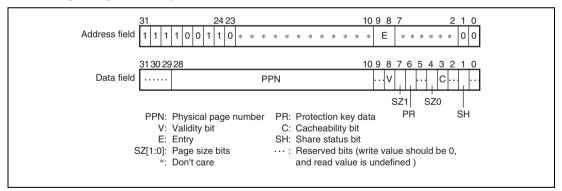

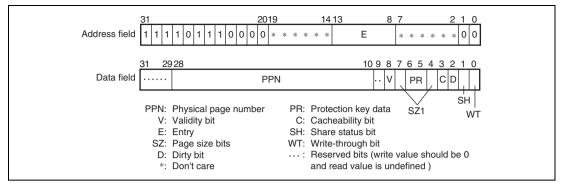

|      | 7.2.1  | Page Table Entry High Register (PTEH)                          | 183 |

|      | 7.2.2  | Page Table Entry Low Register (PTEL)                           | 184 |

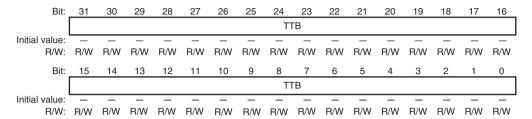

|      | 7.2.3  | Translation Table Base Register (TTB)                          | 185 |

|      | 7.2.4  | TLB Exception Address Register (TEA)                           | 185 |

|      | 7.2.5  | MMU Control Register (MMUCR)                                   | 186 |

|      | 7.2.6  | Page Table Entry Assistance Register (PTEA)                    | 189 |

|      | 7.2.7  | Physical Address Space Control Register (PASCR)                | 189 |

|      | 7.2.8  | Instruction Re-Fetch Inhibit Control Register (IRMCR)          | 191 |

| 7.3  | TLB I  | Functions (TLB Compatible Mode; MMUCR.ME = 0)                  |     |

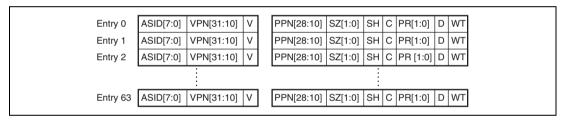

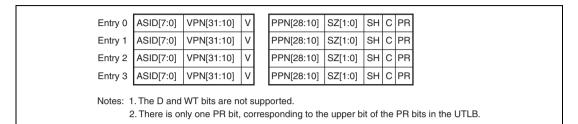

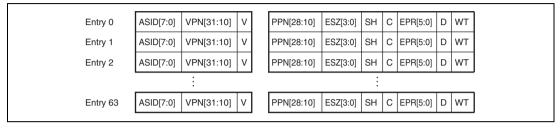

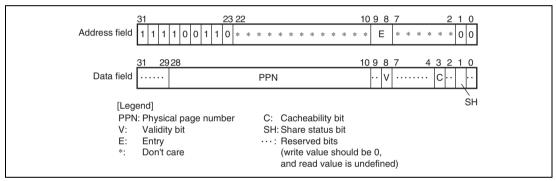

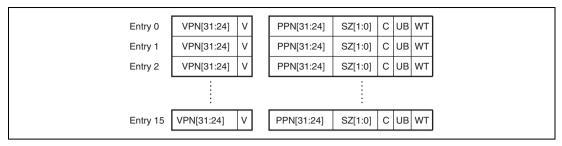

|      | 7.3.1  | Unified TLB (UTLB) Configuration                               | 193 |

|      | 7.3.2  | Instruction TLB (ITLB) Configuration                           | 196 |

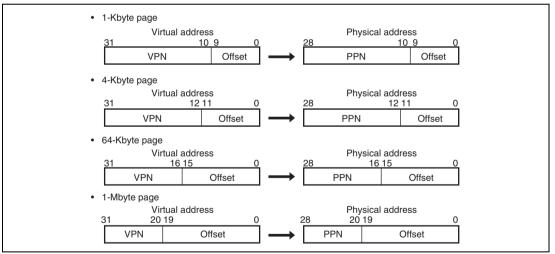

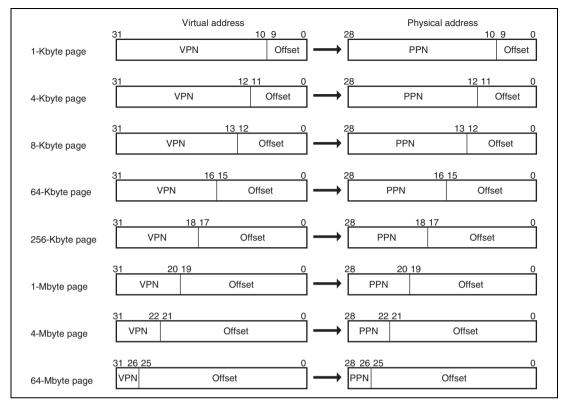

|      | 7.3.3  | Address Translation Method                                     | 196 |

| 7.4  | TLB I  | Functions (TLB Extended Mode; MMUCR.ME = 1)                    | 199 |

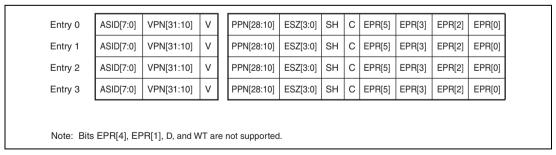

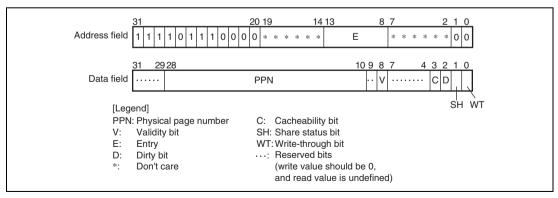

|      | 7.4.1  | Unified TLB (UTLB) Configuration                               | 199 |

|      | 7.4.2  | Instruction TLB (ITLB) Configuration                           | 202 |

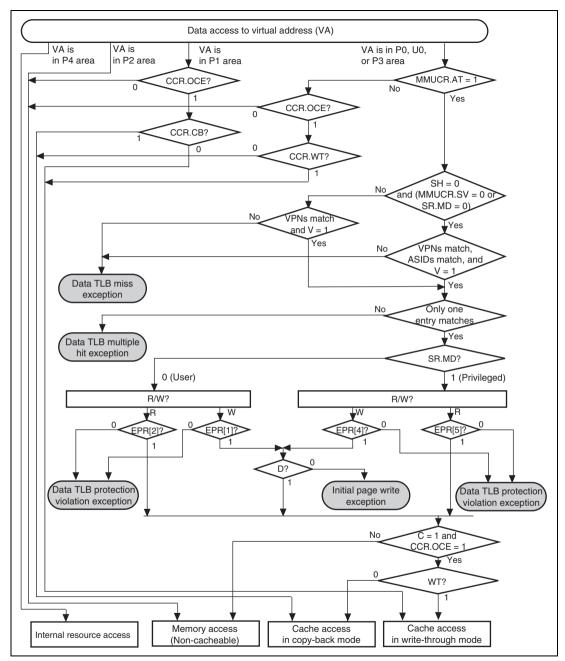

|      | 7.4.3  | Address Translation Method                                     |     |

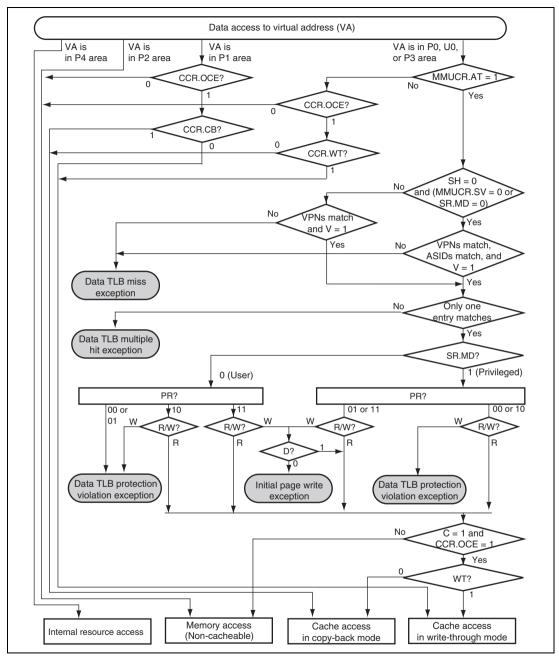

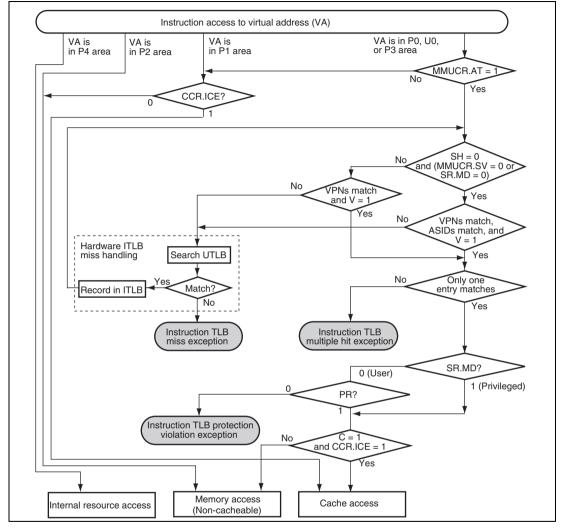

| 7.5  | MMU    | Functions                                                      | 206 |

|      | 7.5.1  | MMU Hardware Management                                        | 206 |

|      | 7.5.2  | MMU Software Management                                        | 206 |

|      | 7.5.3  | MMU Instruction (LDTLB)                                        |     |

|      | 7.5.4  | Hardware ITLB Miss Handling                                    |     |

|      | 7.5.5  | Avoiding Synonym Problems                                      |     |

| 7.6  | MMU    | Exceptions                                                     |     |

|      | 7.6.1  | Instruction TLB Multiple Hit Exception                         |     |

|      | 7.6.2  | Instruction TLB Miss Exception                                 |     |

|      | 7.6.3  | Instruction TLB Protection Violation Exception                 |     |

|      | 7.6.4  | Data TLB Multiple Hit Exception                                |     |

|      | 7.6.5  | Data TLB Miss Exception                                        |     |

|      | 7.6.6  | Data TLB Protection Violation Exception                        |     |

|      | 7.6.7   | Initial Page Write Exception                        |     |

|------|---------|-----------------------------------------------------|-----|

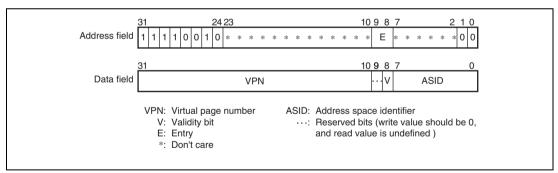

| 7.7  |         | ry-Mapped TLB Configuration                         |     |

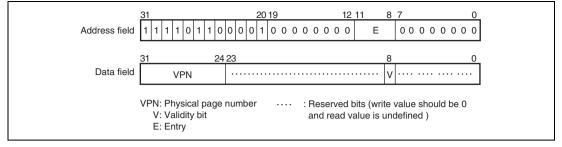

|      | 7.7.1   | ITLB Address Array                                  |     |

|      | 7.7.2   | ITLB Data Array (TLB Compatible Mode)               |     |

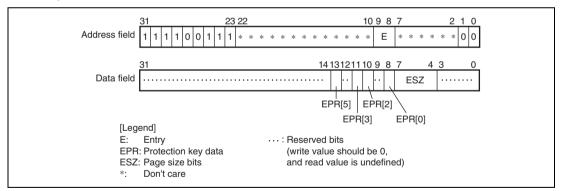

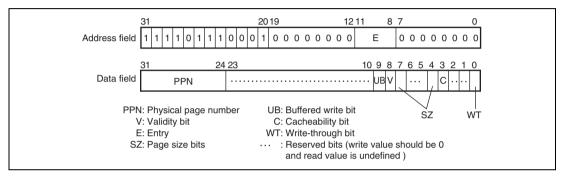

|      | 7.7.3   | ITLB Data Array (TLB Extended Mode)                 |     |

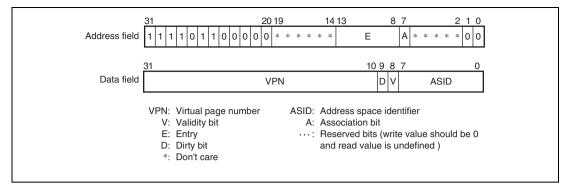

|      | 7.7.4   | UTLB Address Array                                  |     |

|      | 7.7.5   | UTLB Data Array (TLB Compatible Mode)               |     |

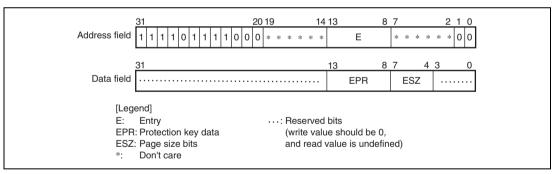

|      | 7.7.6   | UTLB Data Array (TLB Extended Mode)                 |     |

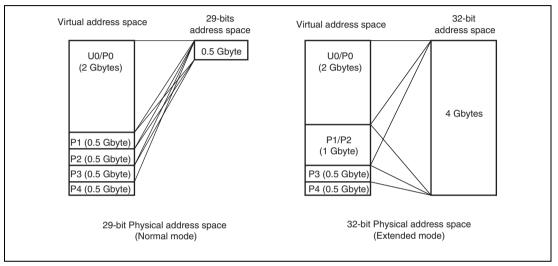

| 7.8  |         | Address Extended Mode                               |     |

|      | 7.8.1   | Overview of 32-Bit Address Extended Mode            |     |

|      | 7.8.2   | Transition to 32-Bit Address Extended Mode          |     |

|      | 7.8.3   | Privileged Space Mapping Buffer (PMB) Configuration |     |

|      | 7.8.4   | PMB Function                                        |     |

|      | 7.8.5   | Memory-Mapped PMB Configuration                     |     |

|      | 7.8.6   | Notes on Using 32-Bit Address Extended Mode         |     |

| 7.9  | Usage   | Notes                                               |     |

|      | 7.9.1   | Note on Using LDTLB Instruction                     | 235 |

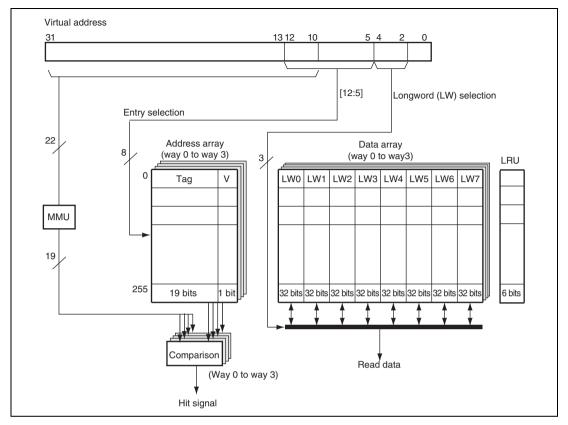

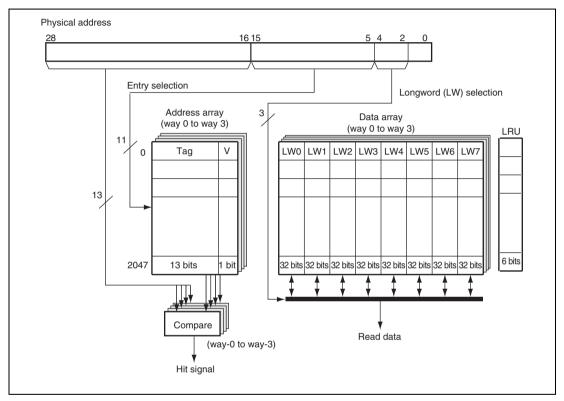

| Sect | ion 8   | Caches                                              | 237 |

| 8.1  | Feature | es                                                  | 237 |

| 8.2  | Registe | er Descriptions                                     | 241 |

|      | 8.2.1   | Cache Control Register (CCR)                        | 242 |

|      | 8.2.2   | Queue Address Control Register 0 (QACR0)            | 244 |

|      | 8.2.3   | Queue Address Control Register 1 (QACR1)            | 245 |

|      | 8.2.4   | On-Chip Memory Control Register (RAMCR)             | 246 |

| 8.3  | Operar  | nd Cache Operation                                  | 248 |

|      | 8.3.1   | Read Operation                                      | 248 |

|      | 8.3.2   | Prefetch Operation                                  | 249 |

|      | 8.3.3   | Write Operation                                     | 250 |

|      | 8.3.4   | Write-Back Buffer                                   | 251 |

|      | 8.3.5   | Write-Through Buffer                                | 251 |

|      | 8.3.6   | OC Two-Way Mode                                     | 252 |

| 8.4  | Instruc | tion Cache Operation                                | 253 |

|      | 8.4.1   | Read Operation                                      | 253 |

|      | 8.4.2   | Prefetch Operation                                  |     |

|      | 8.4.3   | IC Two-Way Mode                                     | 254 |

|      | 8.4.4   | Instruction Cache Way Prediction Operation          | 254 |

| 8.5  | Cache   | Operation Instruction                               |     |

|      | 8.5.1   | Coherency between Cache and External Memory         |     |

|      | 8.5.2   | Prefetch Operation                                  | 256 |

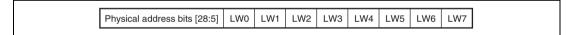

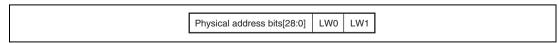

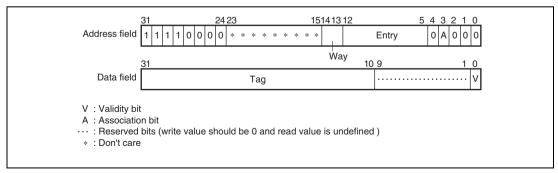

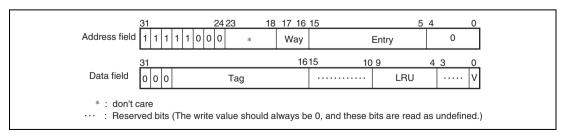

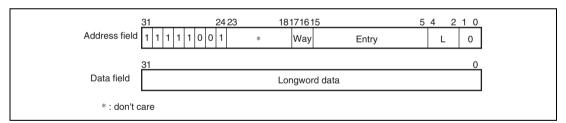

| 8.6  | Memory-Mapped Cache Co    | onfiguration                       | 257 |

|------|---------------------------|------------------------------------|-----|

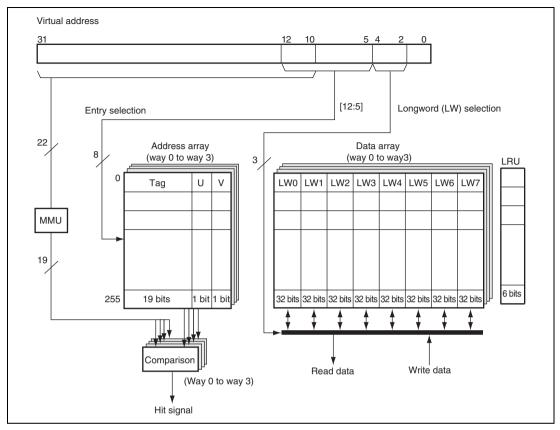

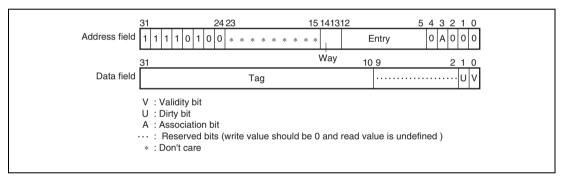

|      | 8.6.1 IC Address Array.   |                                    | 257 |

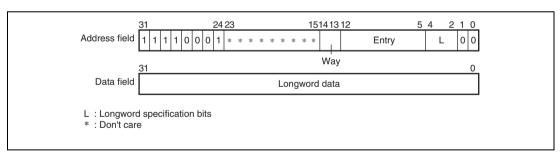

|      | 8.6.2 IC Data Array       |                                    | 259 |

|      | 8.6.3 OC Address Array    |                                    | 260 |

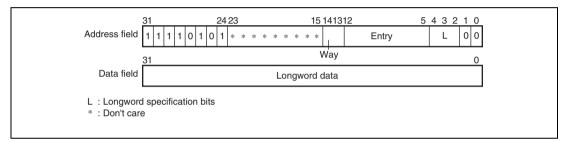

|      | 8.6.4 OC Data Array       |                                    | 261 |

|      | 8.6.5 Memory-Mapped (     | Cache Associative Write Operation  | 262 |

| 8.7  | Store Queues              |                                    | 263 |

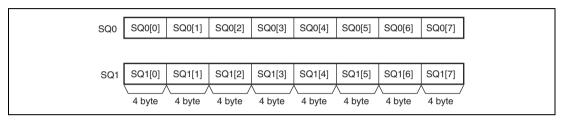

|      | 8.7.1 SQ Configuration.   |                                    | 263 |

|      | 8.7.2 Writing to SQ       |                                    | 263 |

|      | 8.7.3 Transfer to Externa | al Memory                          | 264 |

|      | 8.7.4 Determination of S  | Q Access Exception                 | 265 |

|      | 8.7.5 Reading from SQ.    |                                    | 265 |

| 8.8  | Notes on Using 32-Bit Add | lress Extended Mode                | 266 |

| Sect | ion 9 Secondary Cache     | <b>2</b>                           | 267 |

| 9.1  | -                         |                                    |     |

| 9.2  | Register Descriptions     |                                    | 267 |

|      |                           | Control Register (RAMCR)           |     |

| 9.3  |                           | ation and Operation                |     |

|      | •                         |                                    |     |

|      | _                         | ndary Cache                        |     |

| 9.4  | Configuration of Memory-  | Mapped Secondary Cache             | 275 |

|      | •                         | Address Array                      |     |

|      | -                         | Oata Array                         |     |

| 9.5  |                           |                                    |     |

|      | 9.5.1 Coherency Control   |                                    | 277 |

|      | •                         | tended Mode                        |     |

| Sect | ion 10 On-chip Memor      | ry                                 | 279 |

| 10.1 |                           |                                    |     |

| 10.2 |                           |                                    |     |

|      |                           | Control Register (RAMCR)           |     |

| 10.3 |                           |                                    |     |

|      | 1                         | Access from the CPU                |     |

|      |                           | om the CPU and Access from the FPU |     |

|      | -                         | perHyway Bus Master Module         |     |

| 10.4 |                           | ctions                             |     |

| 10.5 | •                         |                                    |     |

|      | 0                         |                                    |     |

|      | _                         | ferent Pages                       |     |

|      |                           |                                    |     |

|       | 10.5.3   | IL Memory Coherency                                      | 285 |

|-------|----------|----------------------------------------------------------|-----|

|       |          | Sleep Mode                                               |     |

|       |          | 1                                                        |     |

| Secti | on 11    | RS Memory                                                | 287 |

|       |          | ·S                                                       |     |

| 11.2  | Operati  | on                                                       | 287 |

|       | 11.2.1   | Access from the CPU                                      | 287 |

|       | 11.2.2   | Access from the DMAC                                     | 287 |

|       |          |                                                          |     |

| Secti | on 12    | SuperHyway Packet Router                                 | 289 |

| 12.1  | SuperH   | Iyway Bus Connection                                     | 289 |

| 12.2  | SuperH   | Iyway (GPR) Arbitration                                  | 290 |

|       | 12.2.1   | Arbitration of Request Resources                         | 290 |

|       | 12.2.2   | Arbitration of Response Resources                        | 292 |

| 12.3  | Registe  | r Descriptions                                           | 293 |

|       | 12.3.1   | PRI Control Registers (PRPRICR0 to PRPRICR10)            | 294 |

|       | 12.3.2   | LCK Control Register (PRLCKCR)                           | 295 |

|       |          |                                                          |     |

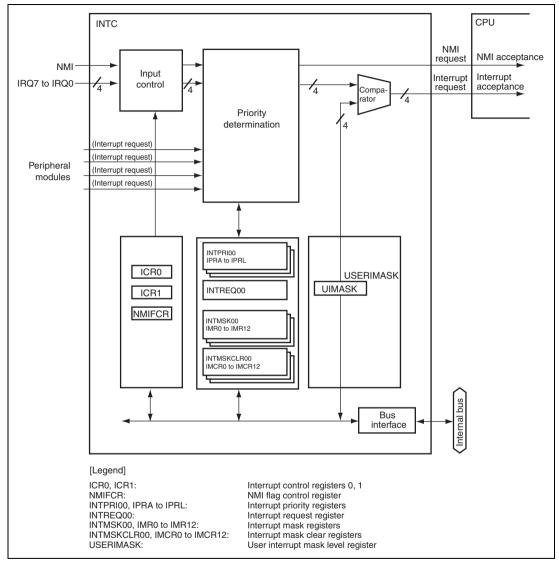

| Secti | on 13    | Interrupt Controller (INTC)                              | 297 |

| 13.1  | Feature  | S                                                        | 297 |

| 13.2  | Input/C  | Output Pins                                              | 299 |

| 13.3  | Registe  | r Descriptions                                           | 299 |

|       | 13.3.1   | Interrupt Control Register 0 (ICR0)                      | 303 |

|       | 13.3.2   | Interrupt Control Register 1 (ICR1)                      | 305 |

|       | 13.3.3   | Interrupt Priority Register 00 (INTPRI00)                | 306 |

|       | 13.3.4   | Interrupt Priority Registers A to L (IPRA to IPRL)       | 307 |

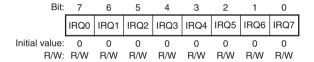

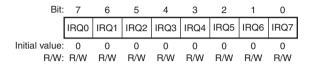

|       | 13.3.5   | Interrupt Request Register 00 (INTREQ00)                 | 309 |

|       | 13.3.6   | Interrupt Mask Register 00 (INTMSK00)                    | 312 |

|       | 13.3.7   | Interrupt Mask Clear Register 00 (INTMSKCLR00)           | 313 |

|       | 13.3.8   | Interrupt Mask Registers 0 to 12 (IMR0 to IMR12)         | 314 |

|       | 13.3.9   | Interrupt Mask Clear Registers 0 to 12 (IMCR0 to IMCR12) | 315 |

|       |          | User Interrupt Mask Level Register (USERIMASK)           |     |

|       | 13.3.11  | NMI Flag Control Register (NMIFCR)                       | 318 |

| 13.4  | Interrup | ot Sources                                               | 319 |

|       | 13.4.1   | NMI Interrupt                                            | 319 |

|       |          | IRQ Interrupts                                           |     |

|       | 13.4.3   | On-Chip Peripheral Module Interrupts                     | 321 |

|       |          | Interrupt Exception Handling and Priority                |     |

| 13.5  |          | on                                                       |     |

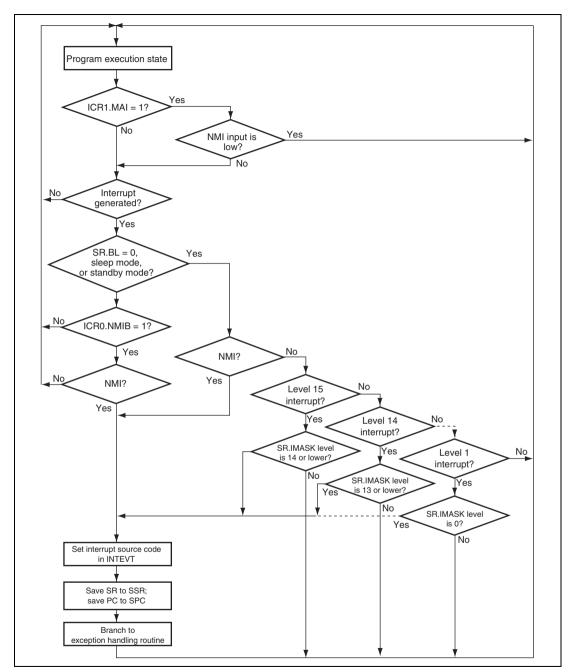

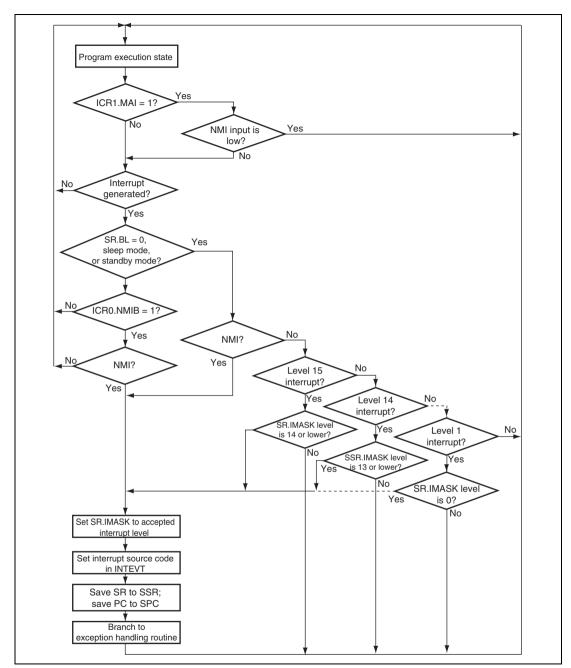

|       | 13.5.1   | Interrupt Sequence                                       | 326 |

|       | 13.5.2        | Multiple Interrupts                                                                                     | 329 |

|-------|---------------|---------------------------------------------------------------------------------------------------------|-----|

|       | 13.5.3        | Interrupt Masking by MAI Bit                                                                            | 329 |

|       | 13.5.4        | Interrupt Disabling Function in User Mode                                                               | 330 |

| 13.6  | Interrup      | ot Response Time                                                                                        | 331 |

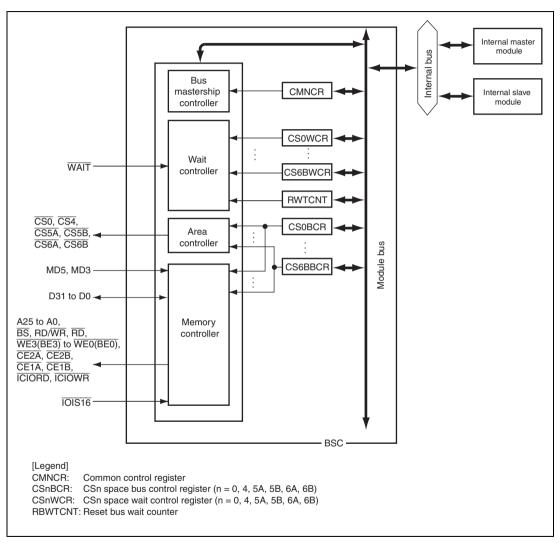

| Secti | on 14         | Bus State Controller (BSC)                                                                              | 333 |

| 14.1  |               | es                                                                                                      |     |

| 14.1  |               | Output Pins                                                                                             |     |

| 14.2  | Area Overview |                                                                                                         |     |

| 14.5  |               | Area Division                                                                                           |     |

|       |               | Address Map                                                                                             |     |

|       |               | Memory Bus Width                                                                                        |     |

|       |               | Data Alignment                                                                                          |     |

| 14.4  |               | or Descriptions                                                                                         |     |

| 14.4  | 14.4.1        | •                                                                                                       |     |

|       | 14.4.1        |                                                                                                         |     |

|       |               |                                                                                                         |     |

|       | 14.4.3        |                                                                                                         |     |

|       |               | CSn Space Wait Control Register (CSnWCR) (n = 0, 4, 5A, 5B, 6A, 6B)<br>Reset Bus Wait Counter (RBWTCNT) |     |

| 1 4 5 |               | ·                                                                                                       |     |

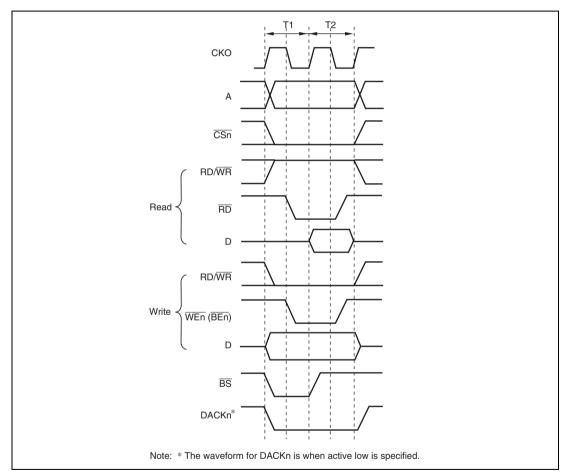

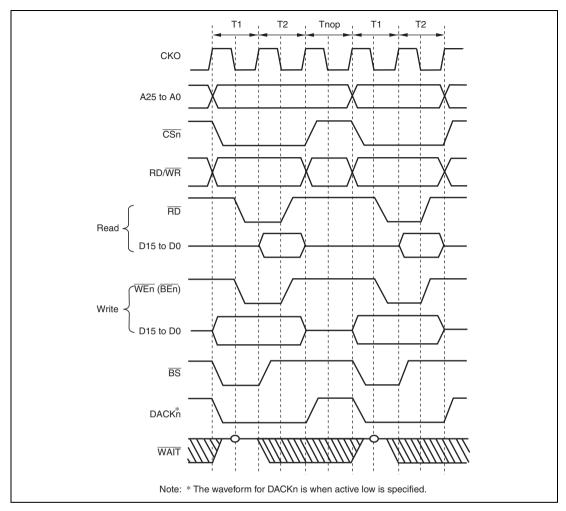

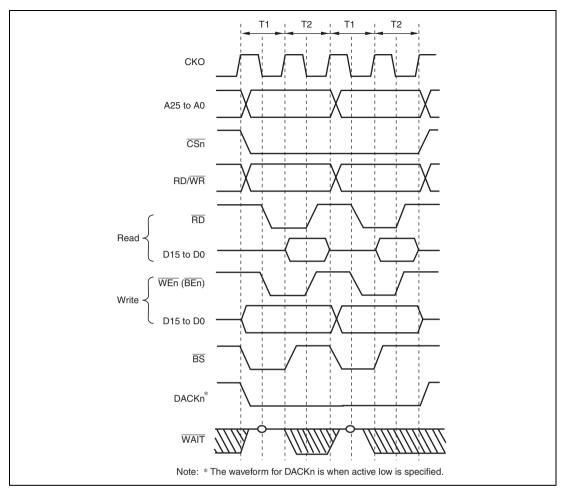

| 14.5  | -             | on                                                                                                      |     |

|       |               | Endian/Access Size and Data Alignment                                                                   |     |

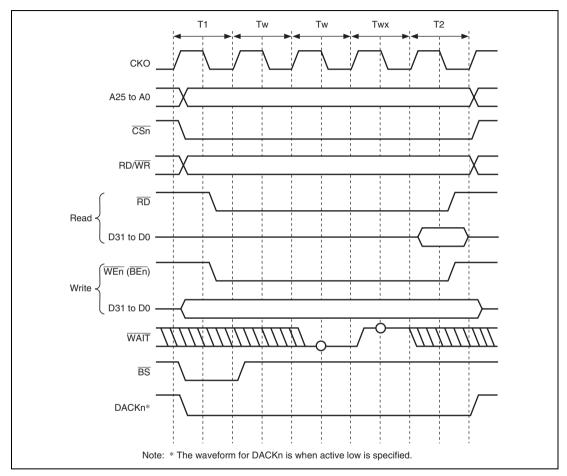

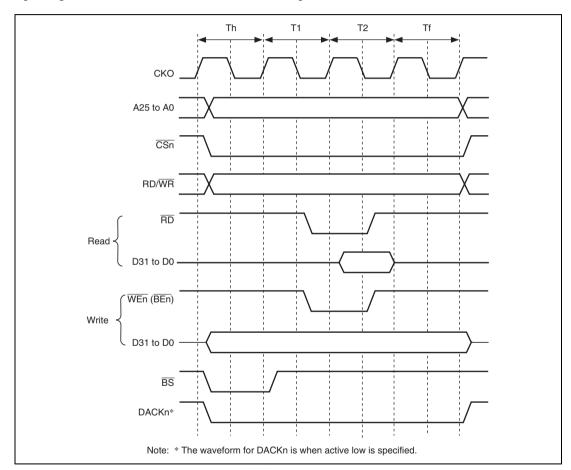

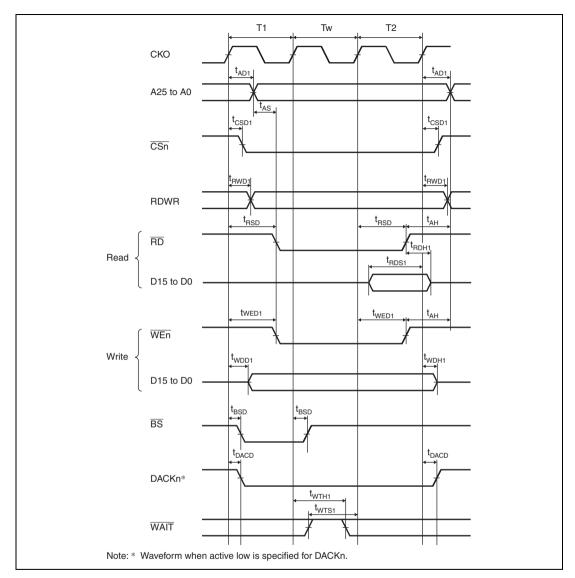

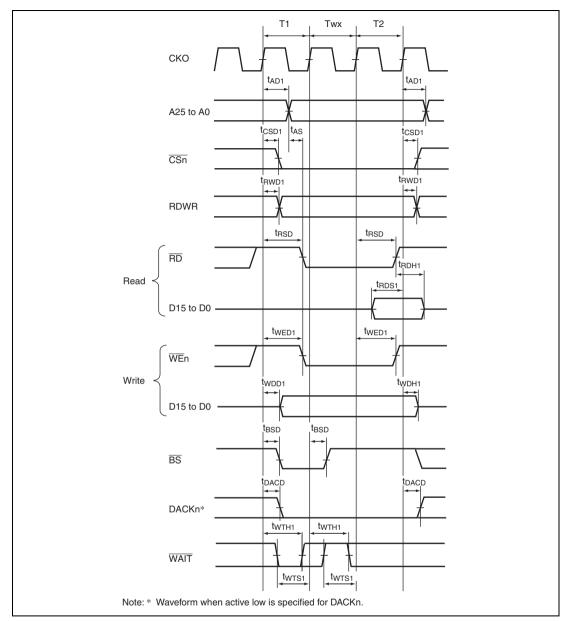

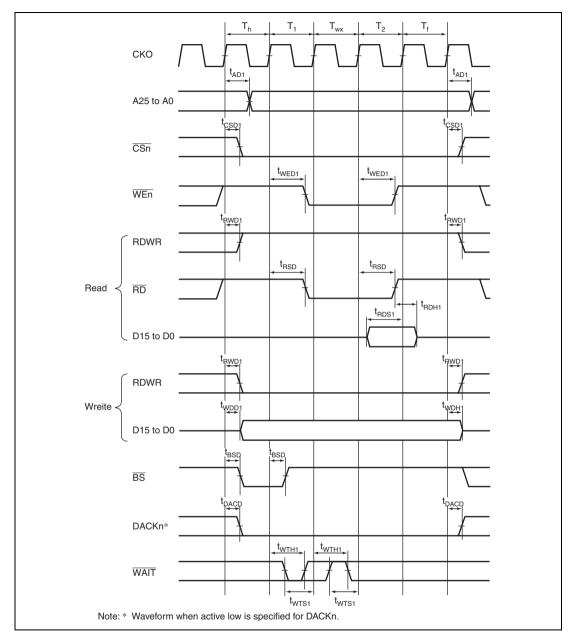

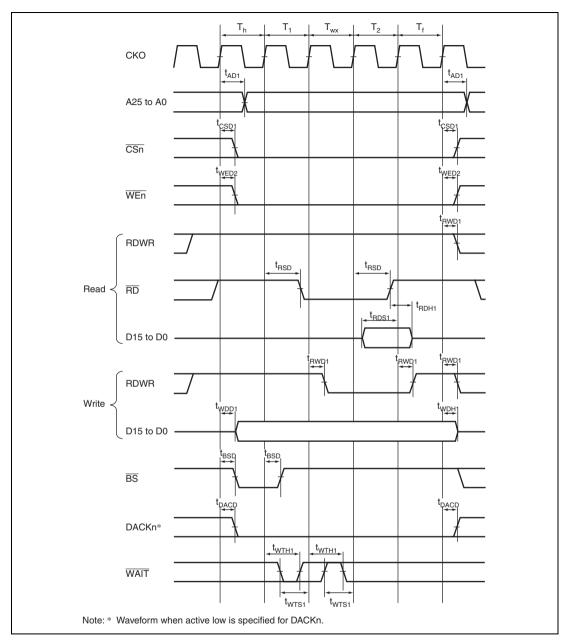

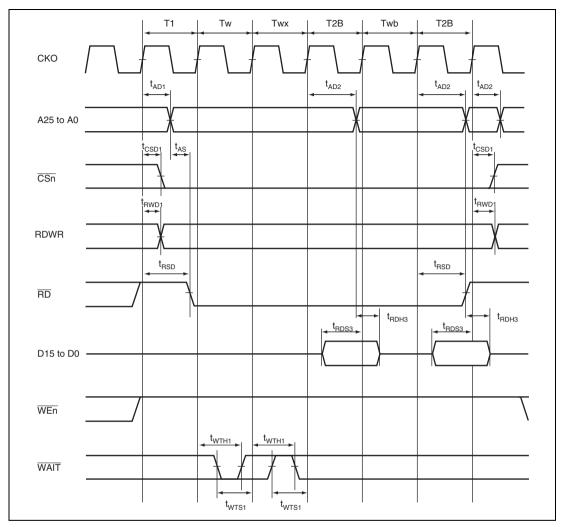

|       |               | Normal Space Interface                                                                                  |     |

|       | 14.5.3        |                                                                                                         |     |

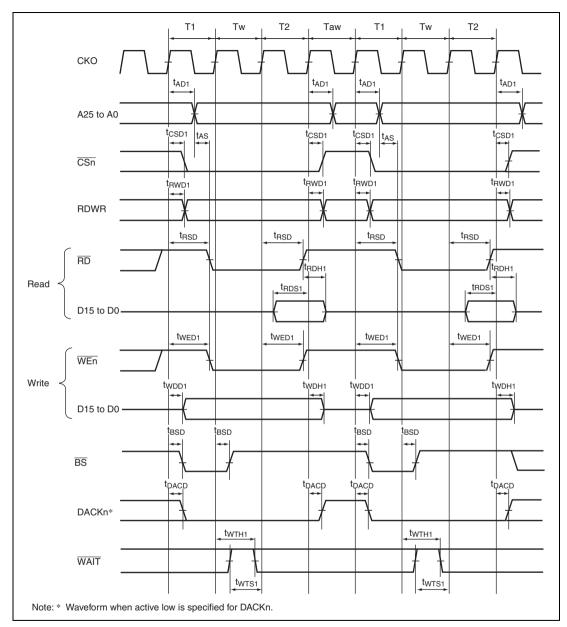

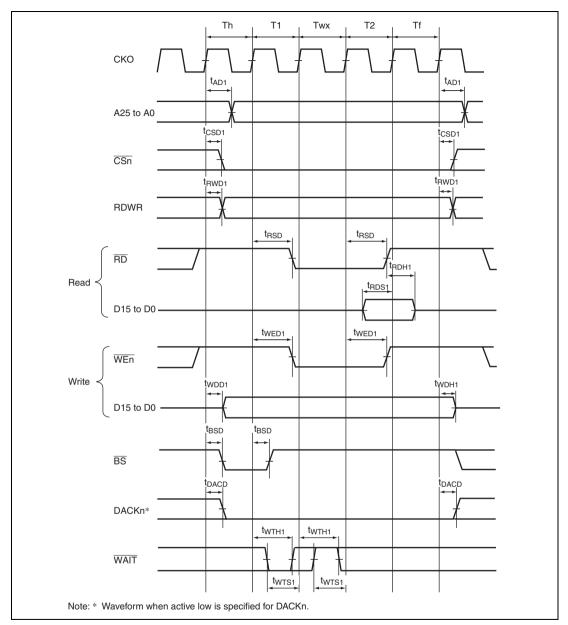

|       |               | CSn Assert Period Extension                                                                             |     |

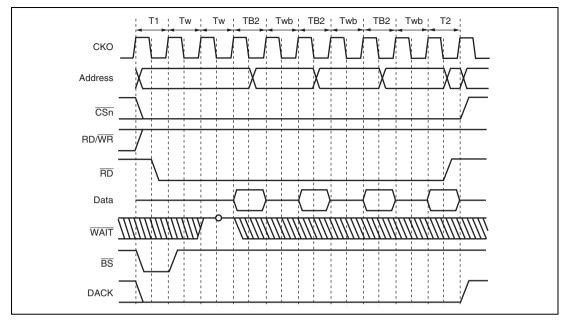

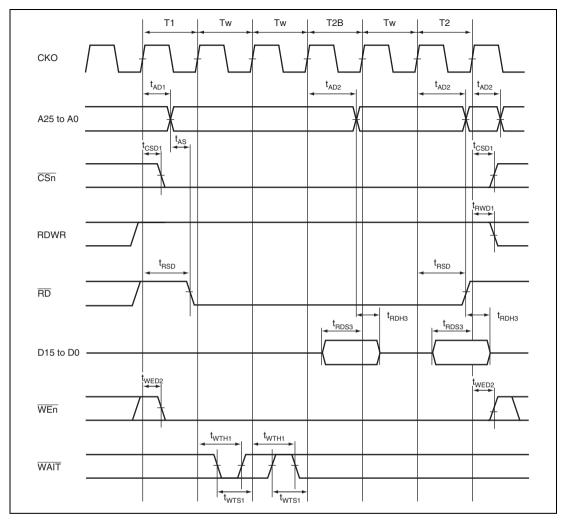

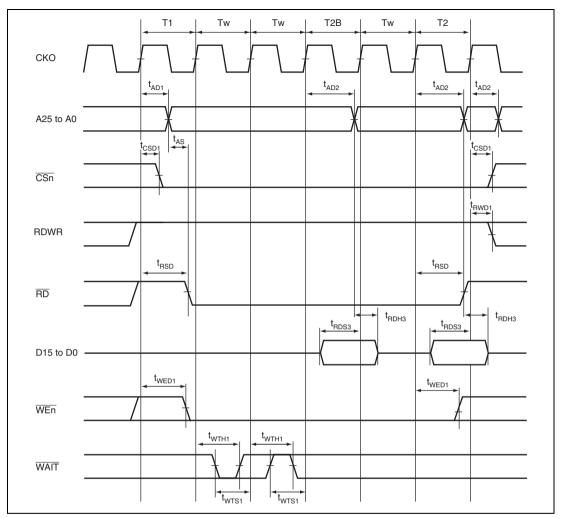

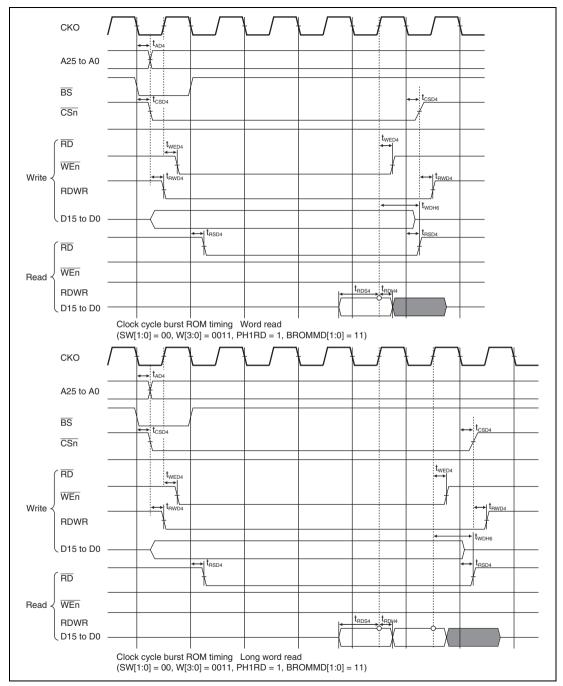

|       |               | Burst ROM Interface.                                                                                    |     |

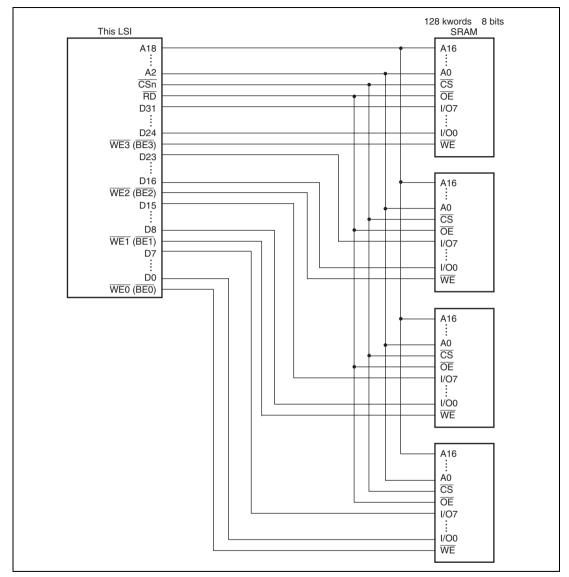

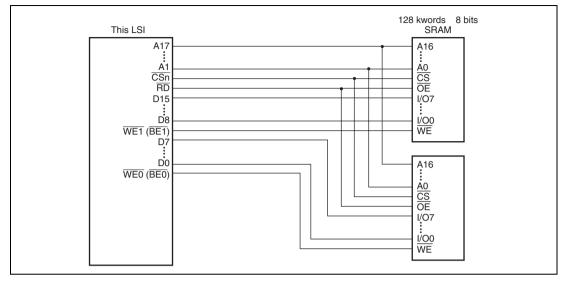

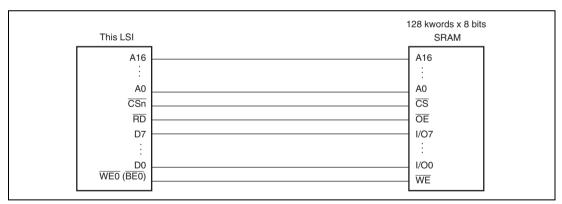

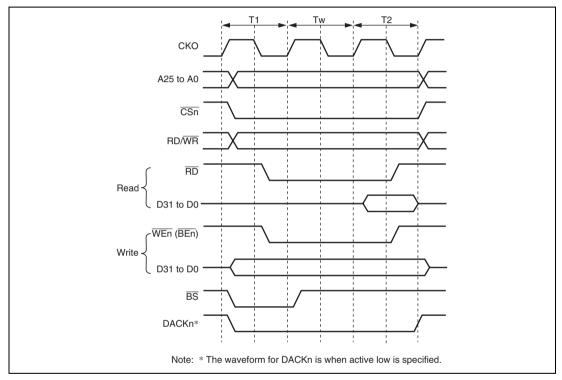

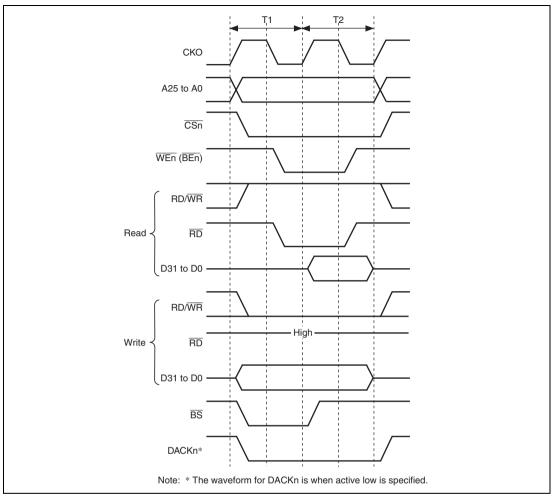

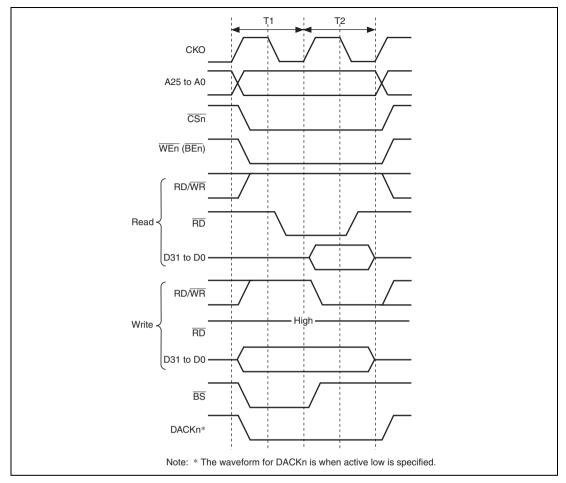

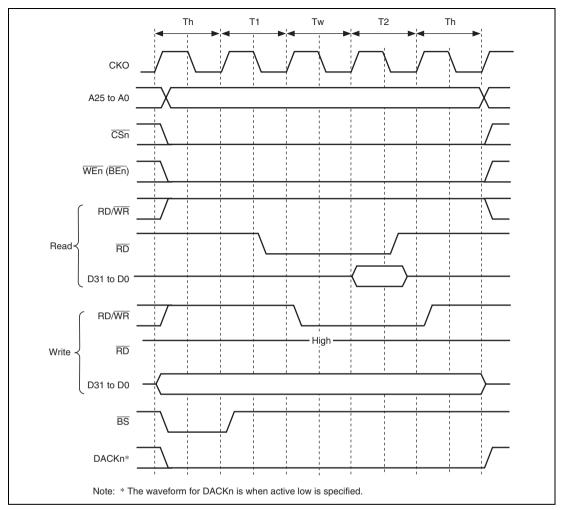

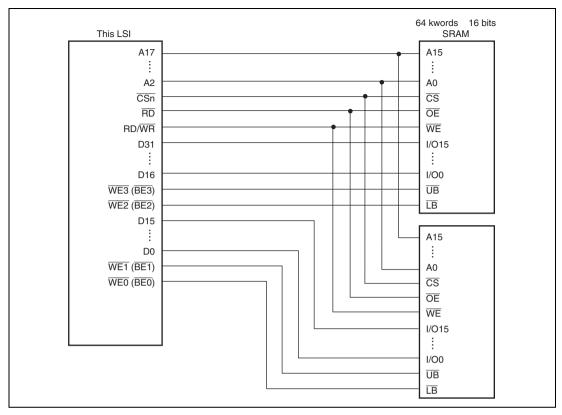

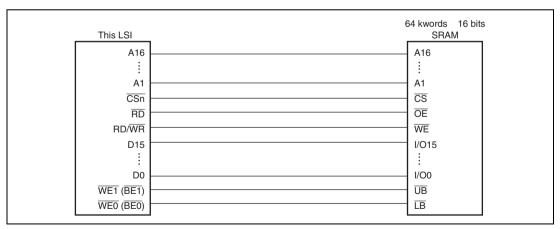

|       |               | SRAM Interface with Byte Selection                                                                      |     |

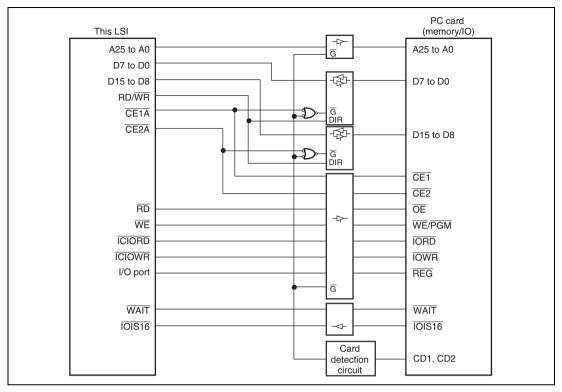

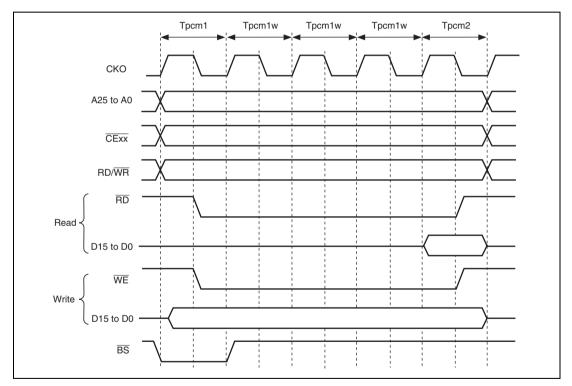

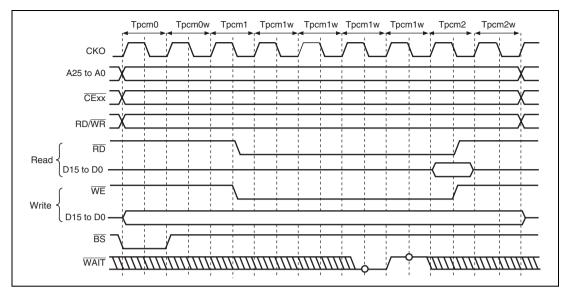

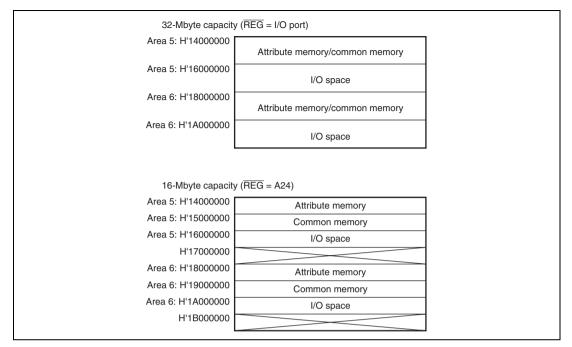

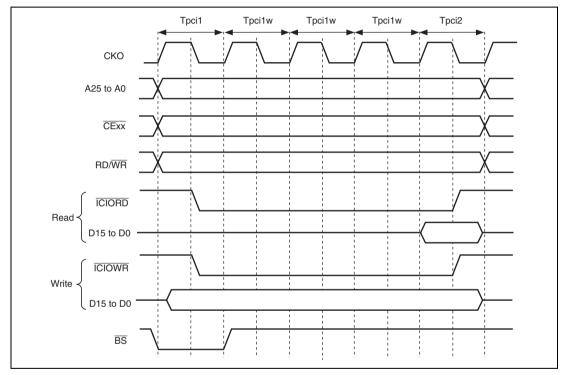

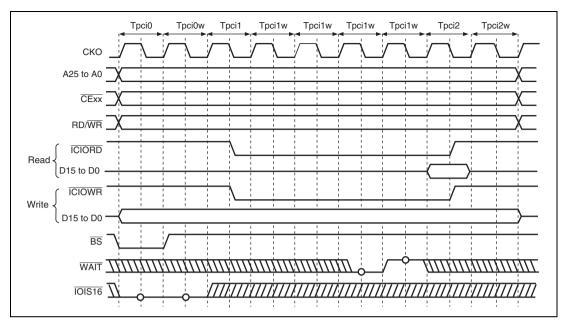

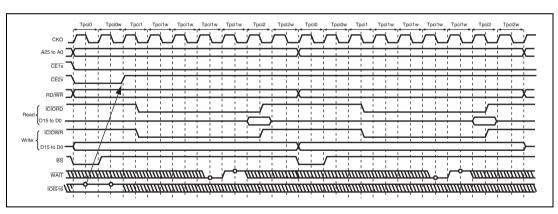

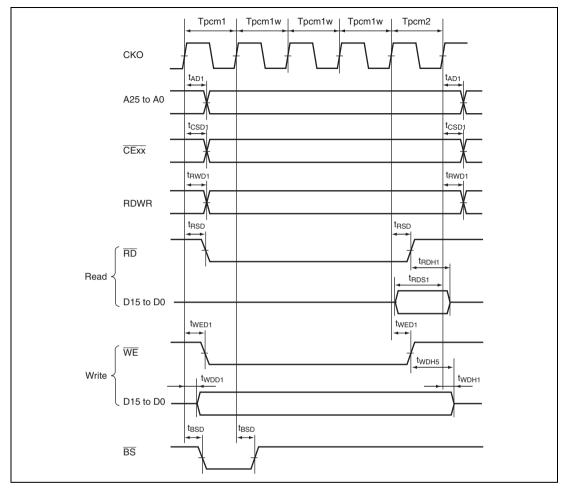

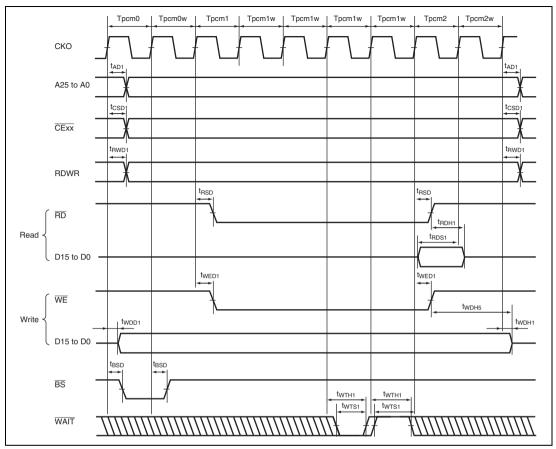

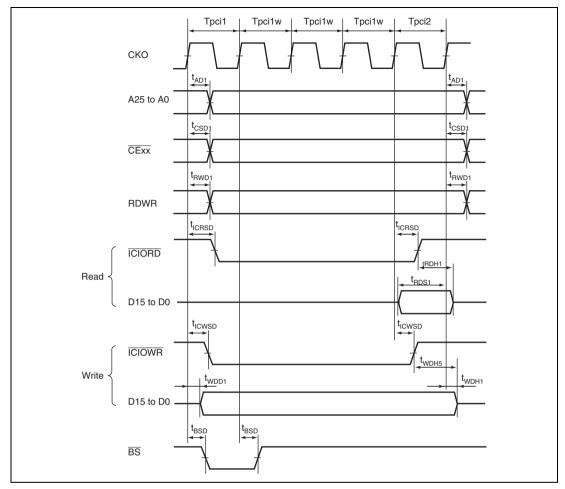

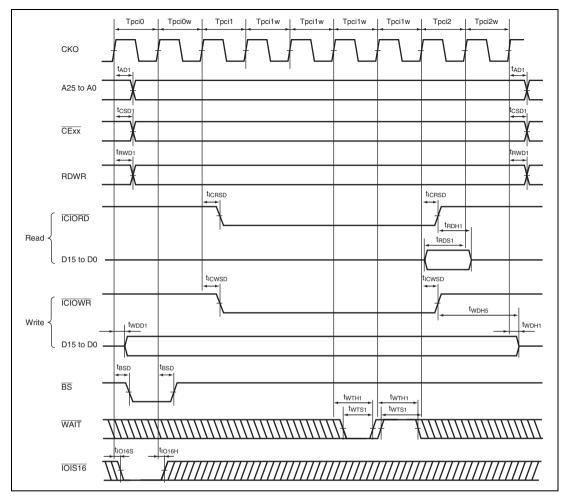

|       |               | PCMCIA Interface                                                                                        |     |

|       |               | Wait between Access Cycles                                                                              |     |

| 14.6  | Others.       |                                                                                                         | 395 |

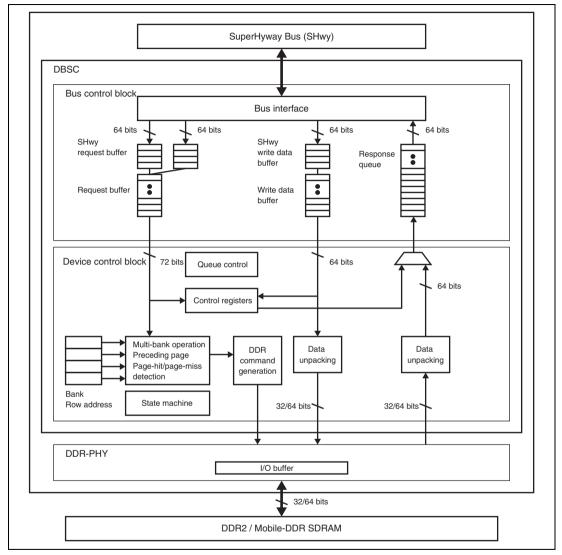

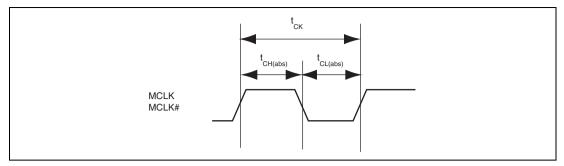

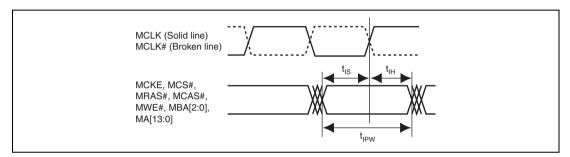

| Secti | on 15         | DDR-SDRAM Bus State Controller (DBSC)                                                                   | 397 |

| 15.1  |               | 98                                                                                                      |     |

| 15.2  |               | Output Pins                                                                                             |     |

| 15.3  | -             | r Descriptions                                                                                          |     |

|       | _             | DBSC SDRAM kind select register (DBKIND)                                                                |     |

|       |               | DBSC Status Register (DBSTATE)                                                                          |     |

|       | 15.3.3        | SDRAM Operation Enable Register (DBEN)                                                                  |     |

|       | 15.3.4        |                                                                                                         |     |

|       | 15.3.5        |                                                                                                         |     |

|       | 15.3.6        | SDRAM Configuration Setting Register (DBCONF)                                                           |     |

|       |               |                                                                                                         |     |

|       | 15.3.7   | SDRAM Timing Register 0 (DBTR0)                                               | 415 |

|-------|----------|-------------------------------------------------------------------------------|-----|

|       | 15.3.8   | SDRAM Timing Register 1 (DBTR1)                                               | 417 |

|       | 15.3.9   | SDRAM Timing Register 2 (DBTR2)                                               | 419 |

|       | 15.3.10  | SDRAM Timing Register 3 (DBTR3)                                               | 421 |

|       | 15.3.11  | SDRAM Refresh Control Register 0 (DBRFPDN0)                                   | 422 |

|       |          | 2 SDRAM Refresh /Power-down Control Register 1 (DBRFPDN1)                     |     |

|       |          | 3 SDRAM Refresh Control Register 2 (DBRFPDN2)                                 |     |

|       | 15.3.14  | SDRAM Refresh Status Register (DBRFSTS)                                       | 427 |

|       | 15.3.15  | 5 SDRAM Mode Setting Register (DBMRCNT)                                       | 428 |

|       |          | 5 DDR-PHY Setting Register (DBPDCNT0)                                         |     |

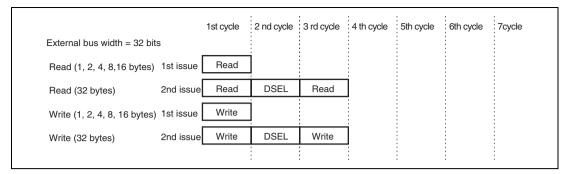

| 15.4  | Data A   | lignment                                                                      | 431 |

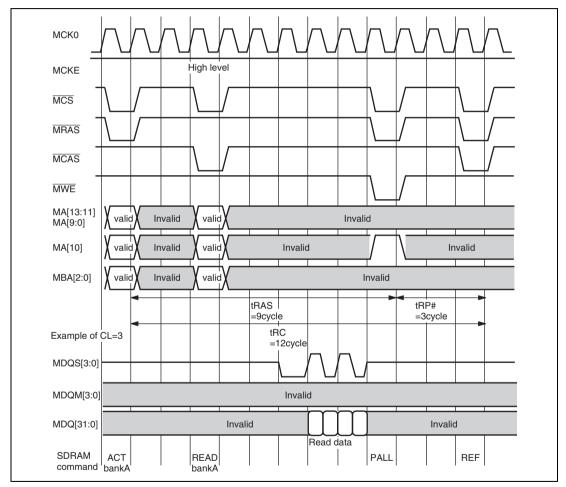

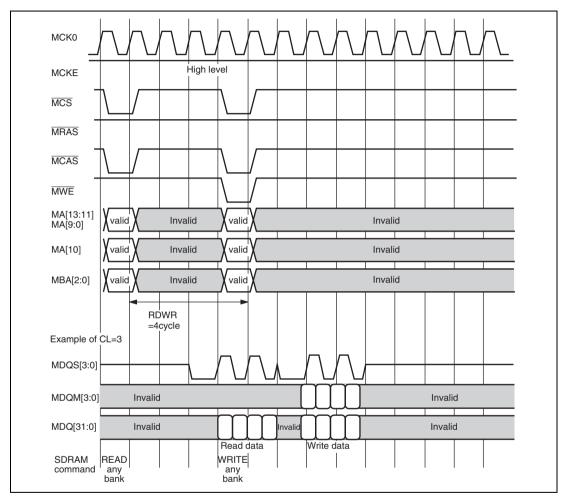

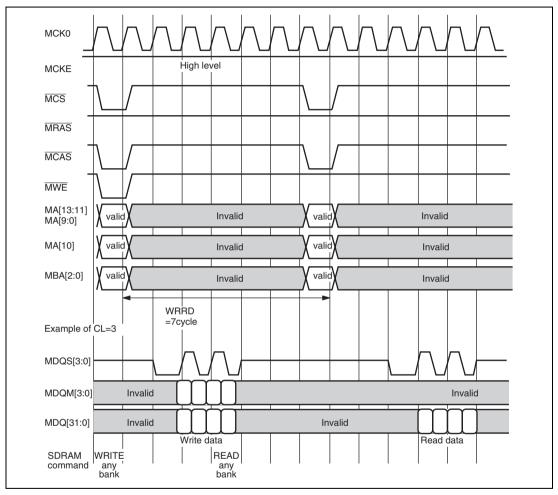

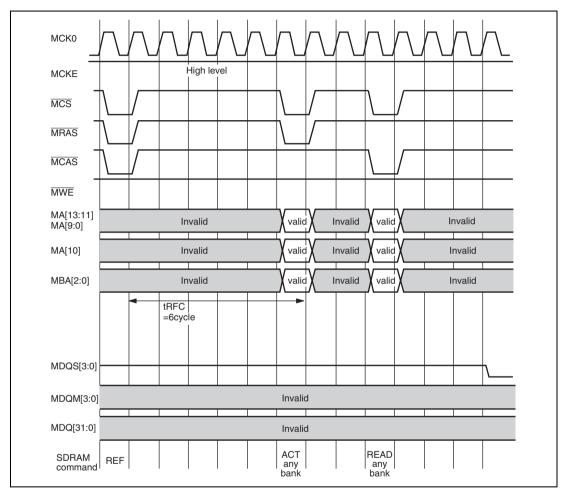

| 15.5  | DBSC     | Operation                                                                     | 441 |

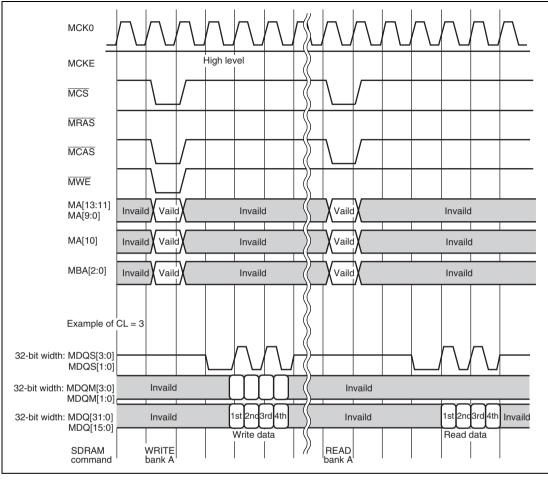

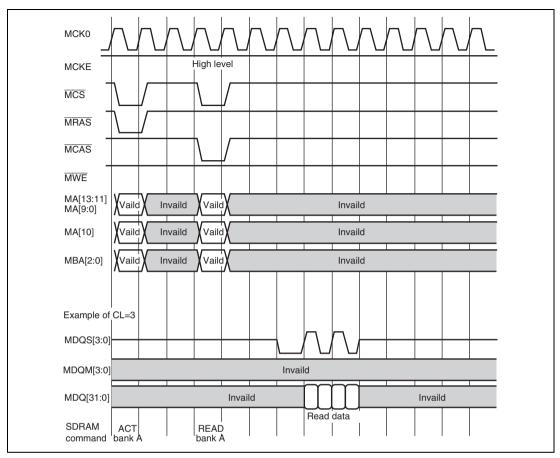

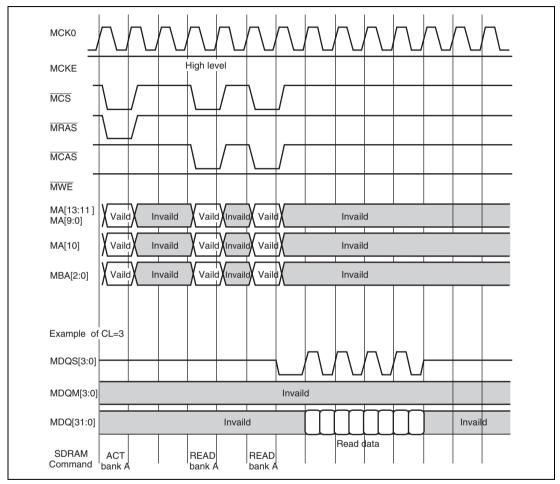

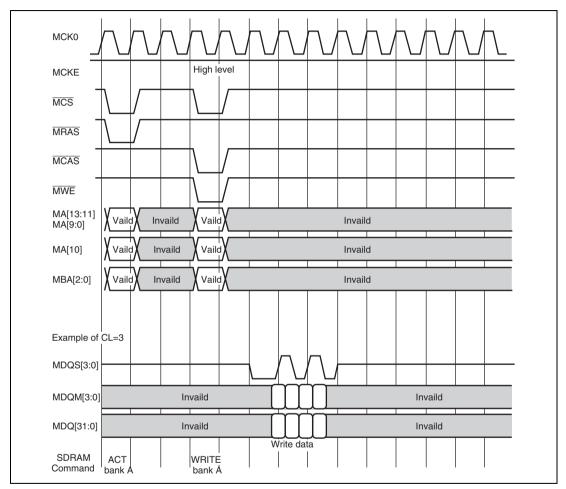

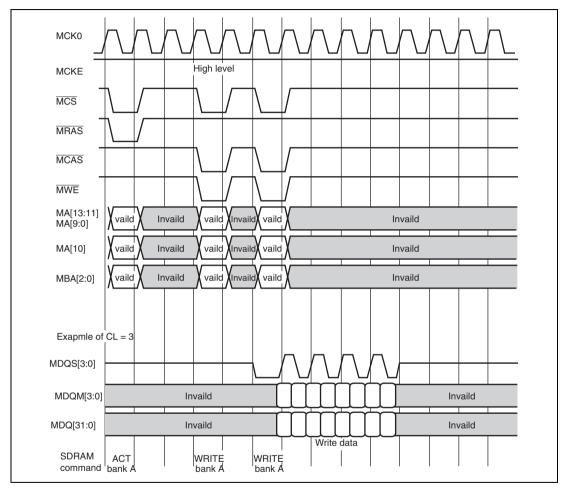

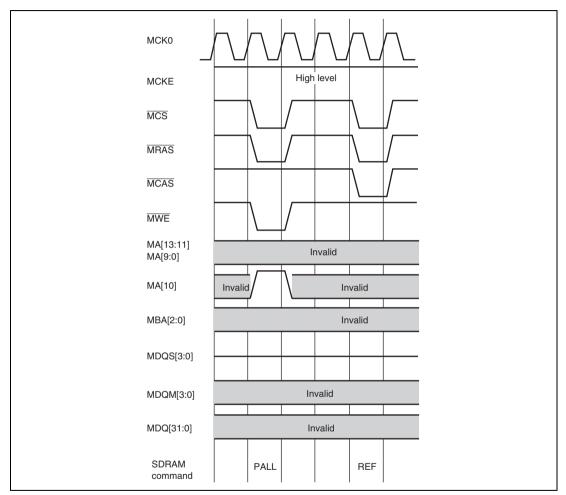

|       | 15.5.1   | Supported SDRAM Commands                                                      | 441 |

|       |          | SDRAM Command Issue                                                           |     |

|       | 15.5.3   | Initialization Sequence                                                       | 445 |

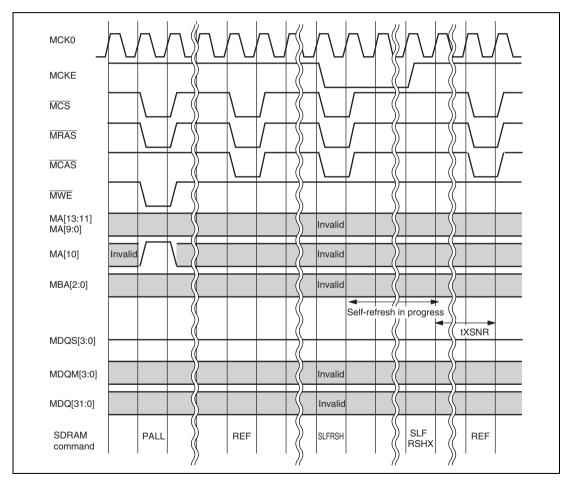

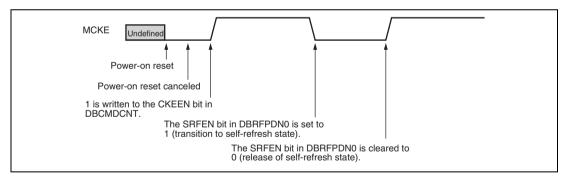

|       |          | Self-Refresh Operation                                                        |     |

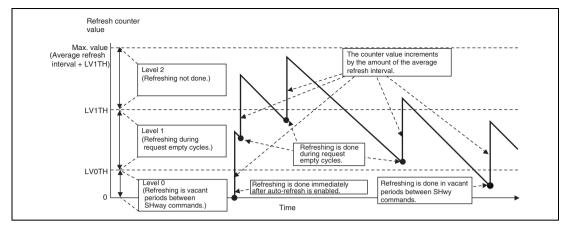

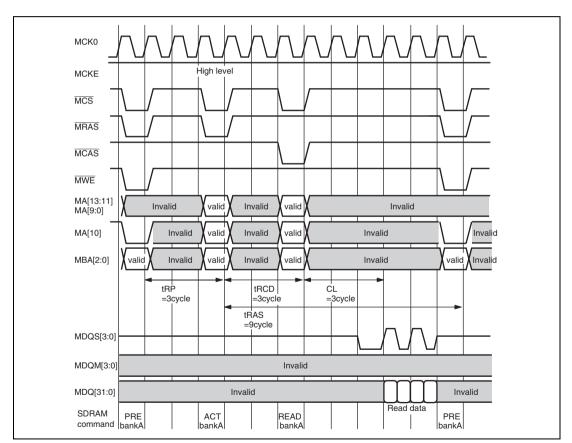

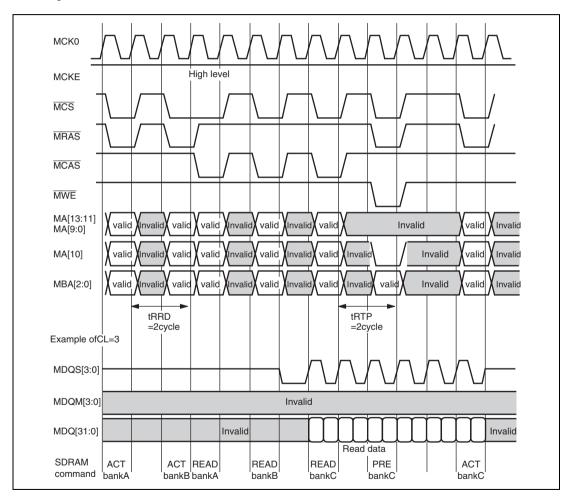

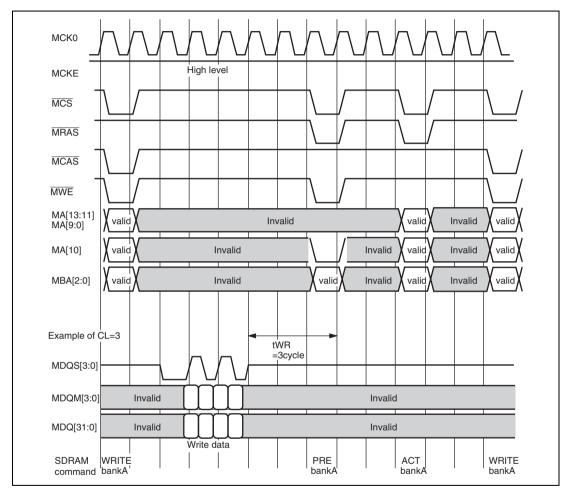

|       |          | Auto-Refresh Operation                                                        |     |

|       |          | Partial Self-Refresh Operation                                                |     |

|       |          | Power-Down Operation                                                          |     |

|       |          | Deep Power-Down Operation                                                     |     |

|       |          | Relation between SDRAM Address Pins and Logical Addresses                     |     |

|       |          | Alignment of the Position of Bank Address                                     |     |

|       |          | SDRAM Access and Timing Constraints                                           |     |

|       |          | 2 Method for Securing Time Required for Operations Including Initialization a |     |

|       |          | Self-Refresh Cancellation                                                     |     |

|       | 15.5.13  | 3 Operation of MCKE Signal                                                    |     |

| 15.6  |          | Notes                                                                         |     |

|       | _        | Important Information Regarding Use of 8-Bank DDR2-SDRAM Products             |     |

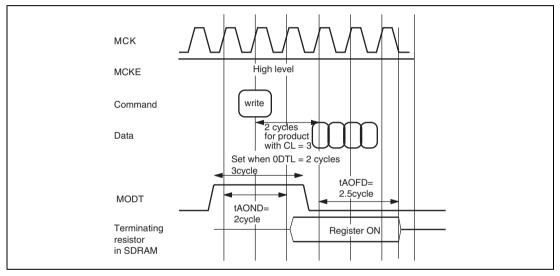

|       |          | Important Information regarding ODT Control Signal Output to SDRAM            |     |

|       |          | Point to Note when Stopping Clocks or Changing the Clock Frequency for        |     |

|       |          | the DBSC                                                                      | 479 |

|       |          |                                                                               |     |

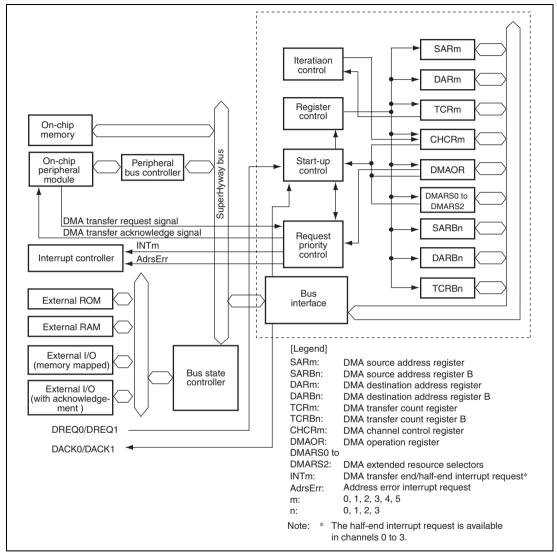

| Secti | ion 16   | Direct Memory Access Controller (DMAC)                                        | 481 |

|       |          | es                                                                            |     |

| 16.2  |          | Output Pins                                                                   |     |

| 16.3  | -        | er Descriptions                                                               |     |

| - 0.0 | U        | DMA Source Address Registers (DMA0_SAR_0 to DMA0_SAR_5,                       |     |

|       | - 0.0.1  | DMA1_SAR_0 to DMA1_SAR_5,)                                                    | 491 |

|       | 16.3.2   | DMA Source Address Registers (DMA0_SARB_0 to DMA0_SARB_3,                     |     |

|       | <b>.</b> | DMA1_SARB_0 to DMA1_SARB_3)                                                   | 491 |

|       |          | 21.2.10.1.00.00 21.110.1100_0/                                                |     |

| 16.3.3 | DMA Destination Address Registers (DMA0_DAR_0 to DMA0_DAR_5,                                                                                                                                                       |                                                                                                   |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

|        | DMA1_DAR_0 to DMA1_DAR_5)                                                                                                                                                                                          | 492                                                                                               |

| 16.3.4 | DMA Destination Address Registers (DMA0_DARB_0 to DMA0_DARB_3,                                                                                                                                                     |                                                                                                   |

|        | DMA1_DARB_0 to DMA1_DARB_3)                                                                                                                                                                                        | 492                                                                                               |

| 16.3.5 | DMA Transfer Count Registers (DMA0_TCR_0 to DMA0_TCR_5,                                                                                                                                                            |                                                                                                   |

|        | DMA1_TCR_0 to DMA1_TCR_5)                                                                                                                                                                                          | 493                                                                                               |

| 16.3.6 | DMA Transfer Count Registers (DMA0_TCRB_0 to DMA0_TCRB_3,                                                                                                                                                          |                                                                                                   |

|        | DMA1_TCRB_0 to DMA1_TCRB_3)                                                                                                                                                                                        | 494                                                                                               |

| 16.3.7 | DMA Channel Control Registers (DMA0_CHCR_0 to DMA0_CHCR_5,                                                                                                                                                         |                                                                                                   |

|        | DMA1_CHCR_0 to DMA1_CHCR_5)                                                                                                                                                                                        | 495                                                                                               |

| 16.3.8 | DMA Operation Register (DMA0_DMAOR, DMA1_DMAOR)                                                                                                                                                                    | 503                                                                                               |

| 16.3.9 | DMA Extended Resource Selectors 0 to 2 (DMA0_DMARS0 to                                                                                                                                                             |                                                                                                   |

|        | DMA0_DMARS2, DMA1_DMARS0 to DMA1_DMARS2)                                                                                                                                                                           | 505                                                                                               |

| Operat | ion                                                                                                                                                                                                                | 508                                                                                               |

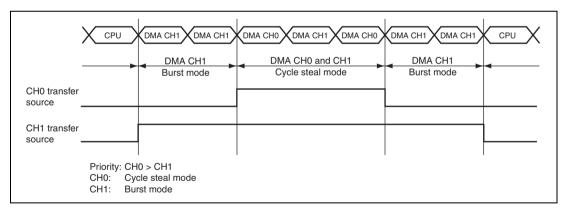

| 16.4.1 | DMA Transfer Requests                                                                                                                                                                                              | 508                                                                                               |

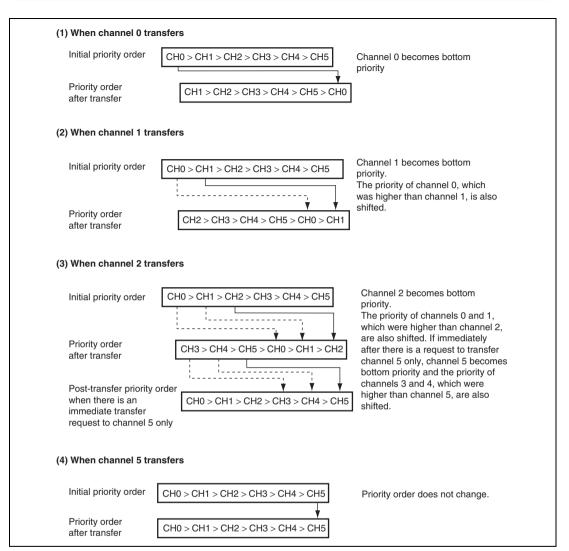

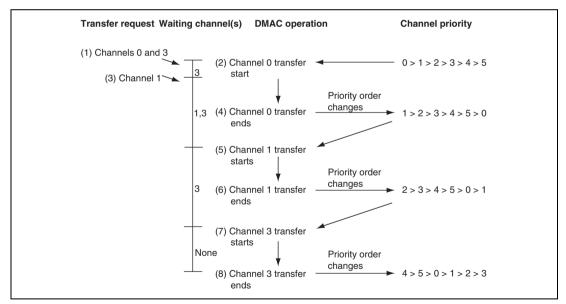

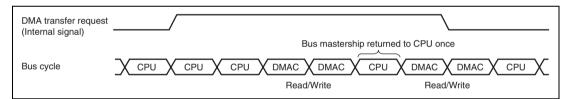

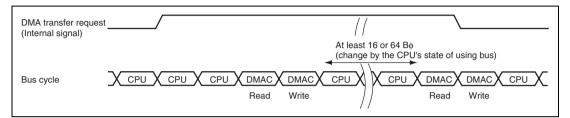

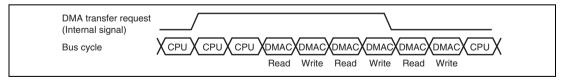

| 16.4.2 | Channel Priority                                                                                                                                                                                                   | 512                                                                                               |

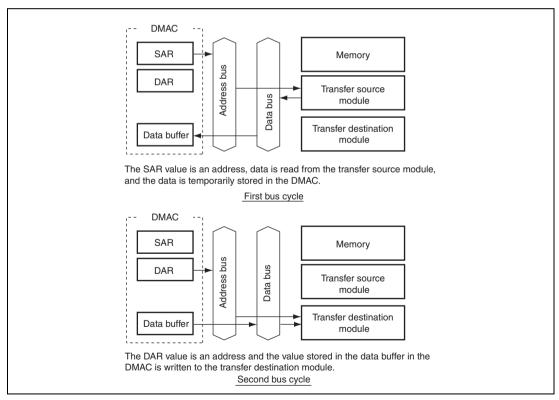

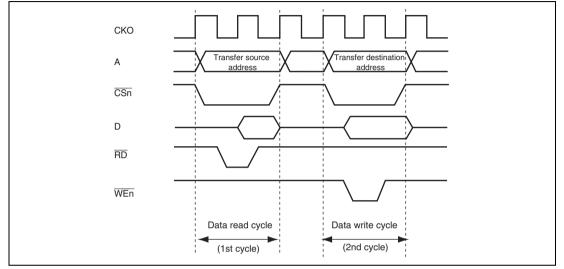

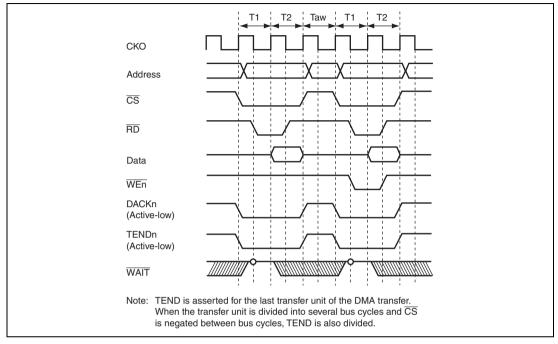

| 16.4.3 | DMA Transfer Types                                                                                                                                                                                                 | 515                                                                                               |

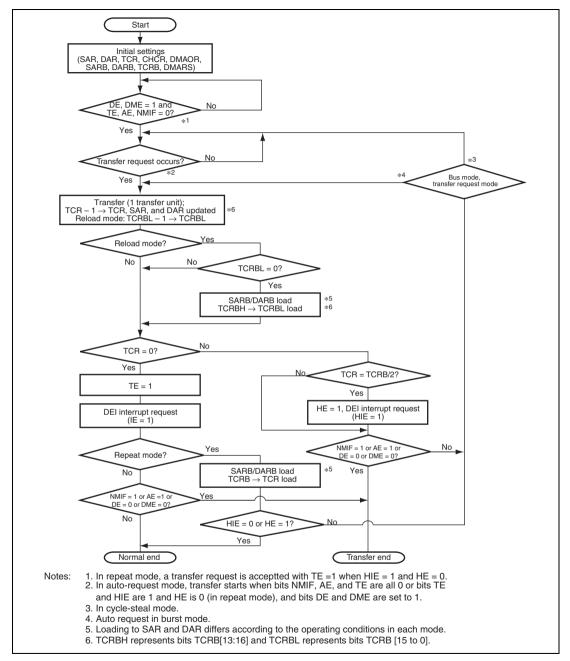

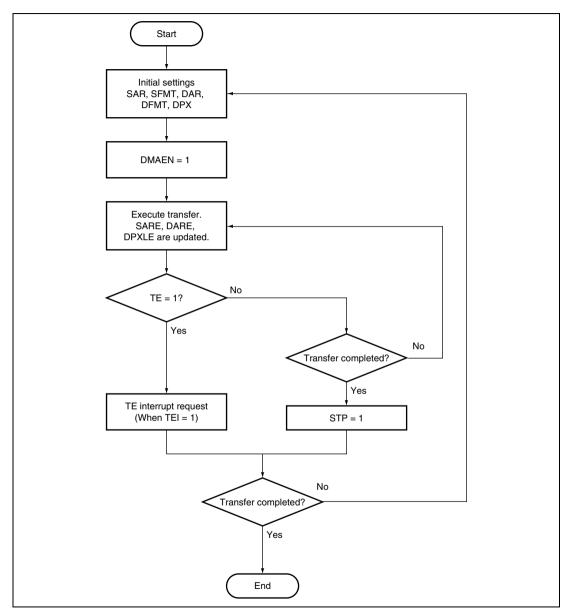

| 16.4.4 | DMA Transfer Flow                                                                                                                                                                                                  | 522                                                                                               |

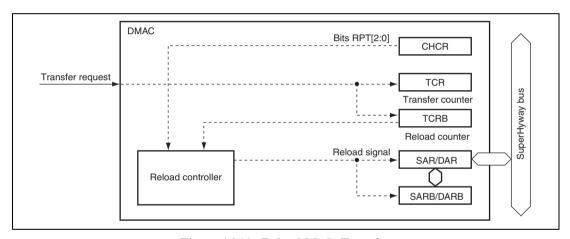

| 16.4.5 | Repeat Mode Transfer                                                                                                                                                                                               | 524                                                                                               |

| 16.4.6 | Reload Mode Transfer                                                                                                                                                                                               | 525                                                                                               |

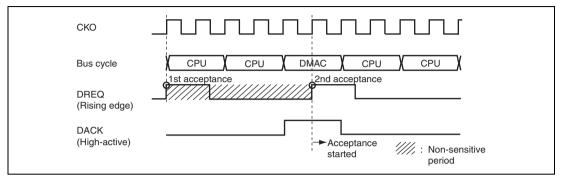

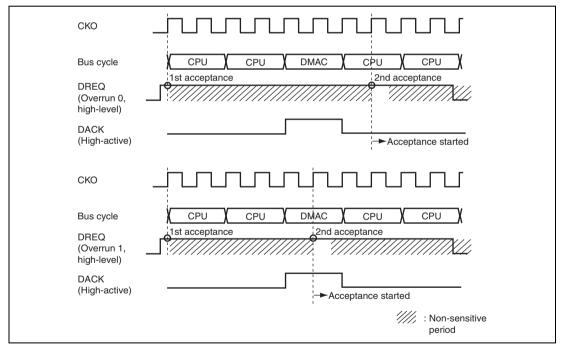

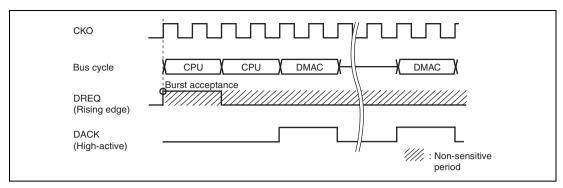

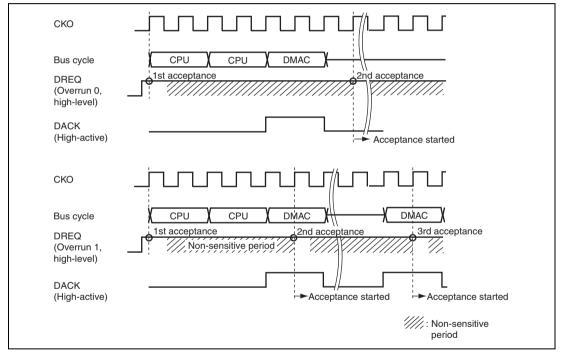

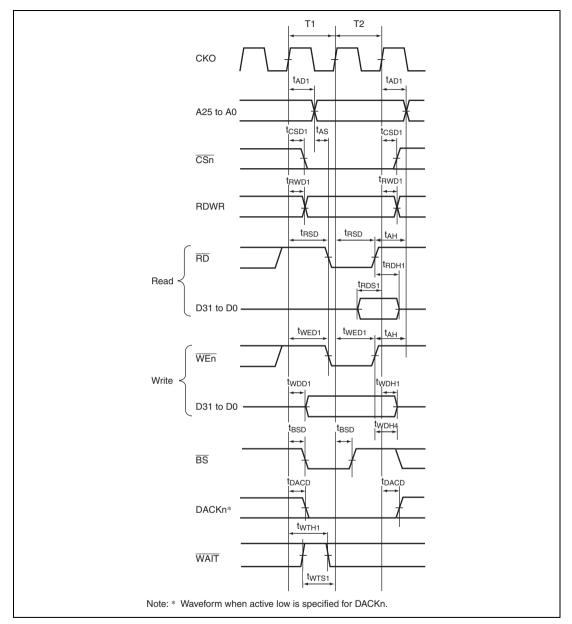

| 16.4.7 | DREQ Pin Sampling Timing                                                                                                                                                                                           | 526                                                                                               |

| Usage  | Notes                                                                                                                                                                                                              | 529                                                                                               |

| 16.5.1 | DMA Transfer for Peripheral Modules                                                                                                                                                                                | 529                                                                                               |

| 16.5.2 | Module Stop                                                                                                                                                                                                        | 529                                                                                               |

|        |                                                                                                                                                                                                                    |                                                                                                   |

| 16.5.4 | Notes on Burst Mode Transfer                                                                                                                                                                                       | 529                                                                                               |

| 16.5.5 | Notes on Setting of DMA Extended Resource Selectors                                                                                                                                                                | 529                                                                                               |

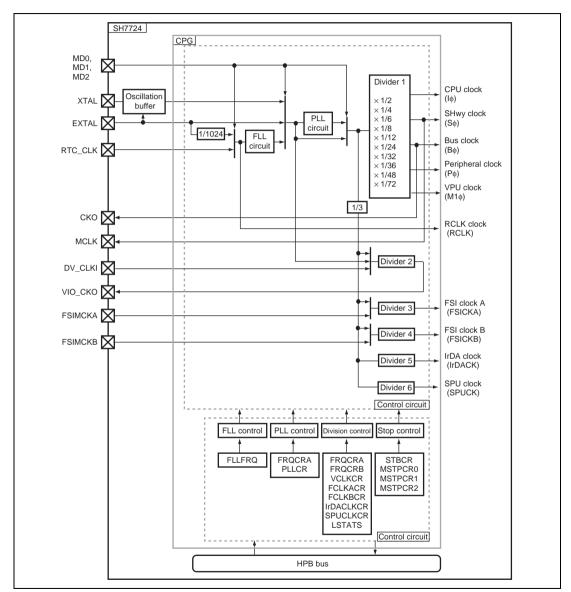

| ion 17 | Clock Pulse Generator (CPG)                                                                                                                                                                                        | 531                                                                                               |

|        |                                                                                                                                                                                                                    |                                                                                                   |

|        |                                                                                                                                                                                                                    |                                                                                                   |

|        |                                                                                                                                                                                                                    |                                                                                                   |

| -      | <u> </u>                                                                                                                                                                                                           |                                                                                                   |

|        |                                                                                                                                                                                                                    |                                                                                                   |

| _      | •                                                                                                                                                                                                                  |                                                                                                   |

|        |                                                                                                                                                                                                                    |                                                                                                   |

|        |                                                                                                                                                                                                                    |                                                                                                   |

|        |                                                                                                                                                                                                                    |                                                                                                   |

|        |                                                                                                                                                                                                                    |                                                                                                   |

|        |                                                                                                                                                                                                                    |                                                                                                   |

|        | 16.3.4 16.3.5 16.3.6 16.3.7 16.3.8 16.3.9 Operat 16.4.1 16.4.2 16.4.3 16.4.4 16.4.5 16.4.6 16.4.7 Usage 16.5.1 16.5.2 16.5.3 16.5.4 16.5.5 ion 17 Feature Block Input/C Clock Cock Cock Cock Cock Cock Cock Cock C | 16.3.4 DMA Destination Address Registers (DMA0_DARB_0 to DMA0_DARB_3, DMA1_DARB_0 to DMA1_DARB_3) |

|       | 17.5.7  | IrDA Clock Frequency Control Register (IrDACLKCR)    | . 547 |

|-------|---------|------------------------------------------------------|-------|

|       | 17.5.8  | SPU clock frequency control register (SPUCLKCR)      | . 548 |

|       | 17.5.9  | FLL Multiplication Register (FLLFRQ)                 | . 549 |

|       | 17.5.10 | Frequency change status register (LSTATS)            | . 550 |

| 17.6  |         | ng Frequency                                         |       |

|       |         | Changing Multiplication Ratio of PLL Circuit         |       |

|       | 17.6.2  | Changing Division Ratio                              | . 551 |

|       | 17.6.3  | Changing Clock Operating Mode                        | . 552 |

|       | 17.6.4  | Turning On/Off PLL Circuit                           | . 552 |

|       | 17.6.5  | Changing Multiplication Ratio of FLL Circuit         | . 552 |

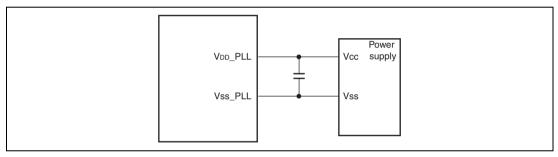

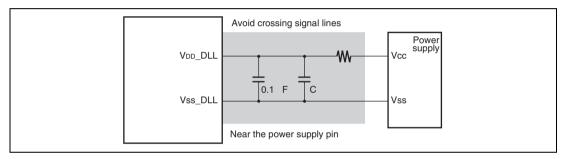

| 17.7  | Notes o | on Board Design                                      | . 553 |

| Secti | on 18   | Reset and Power-Down Modes                           | 555   |

| 18.1  | Feature | S                                                    | . 555 |

|       |         | Division of Power-Supply Areas                       |       |

|       |         | Types of Resets and Power-Down Modes                 |       |

| 18.2  |         | Output Pins                                          |       |

| 18.3  | -       | r Descriptions                                       |       |

|       | 18.3.1  | Standby Control Register (STBCR)                     | . 559 |

|       | 18.3.2  | Module Stop Register 0 (MSTPCR0)                     |       |

|       |         | Module Stop Register 1 (MSTPCR1)                     |       |

|       |         | Module Stop Register 2 (MSTPCR2)                     |       |

|       | 18.3.5  | Boot Address Register (BAR)                          | . 572 |

| 18.4  | Operati | on                                                   | . 574 |

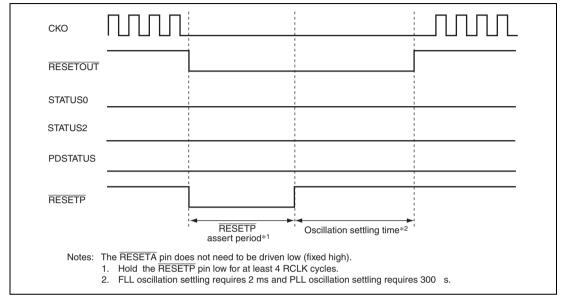

|       | 18.4.1  | Reset                                                | . 574 |

|       | 18.4.2  | Sleep Mode                                           | . 574 |

|       | 18.4.3  | Software Standby Mode                                | . 576 |

|       | 18.4.4  | Module Standby Function                              | . 577 |

|       | 18.4.5  | U-Standby Mode                                       | . 578 |

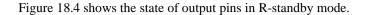

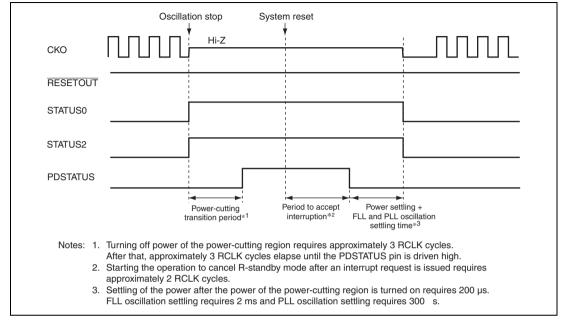

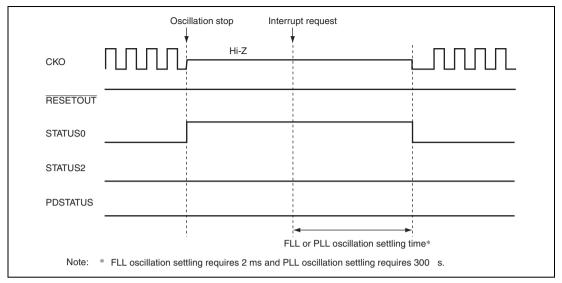

|       | 18.4.6  | R-Standby Mode                                       | . 579 |

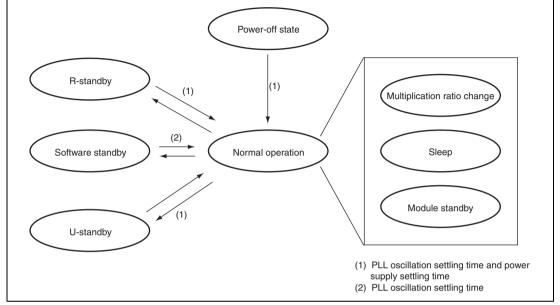

|       | 18.4.7  | Mode Transitions                                     | . 582 |

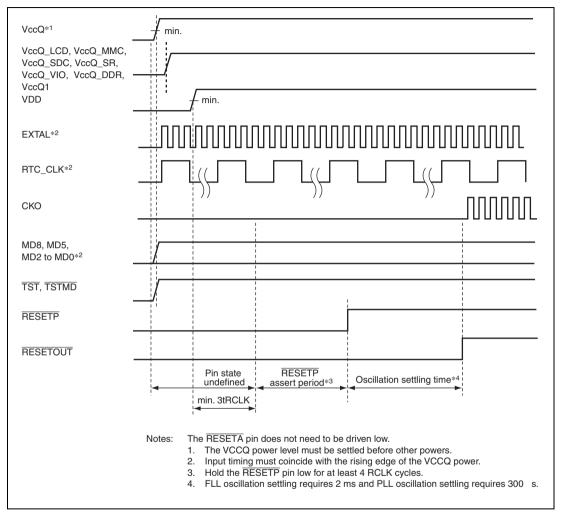

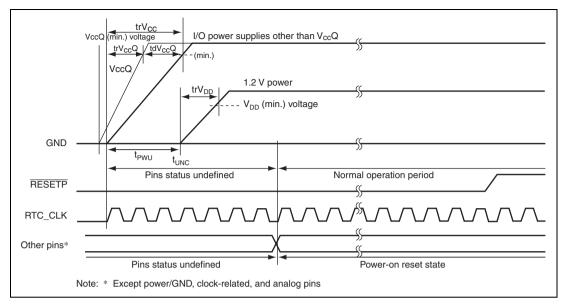

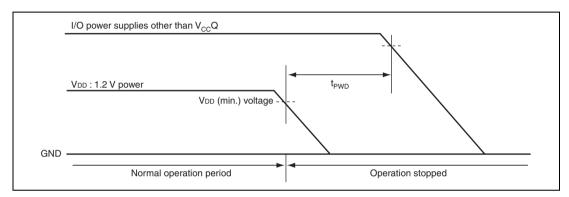

|       | 18.4.8  | Power-On Sequence                                    | . 583 |

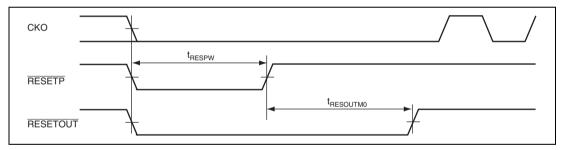

|       | 18.4.9  | Output Pins Change Timing                            | . 584 |

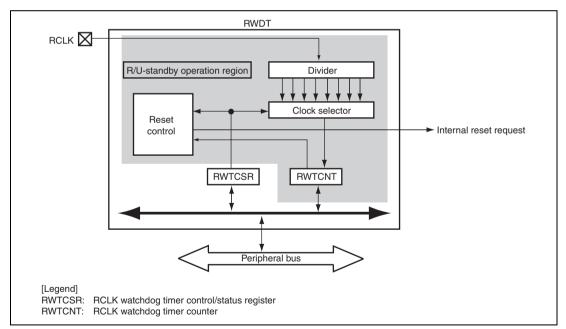

| Secti | on 19   | RCLK Watchdog Timer (RWDT)                           | 589   |

| 19.1  |         | S                                                    |       |

| 19.2  | Input/C | Output Pins for RWDT                                 | . 590 |

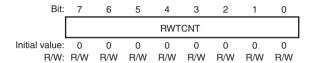

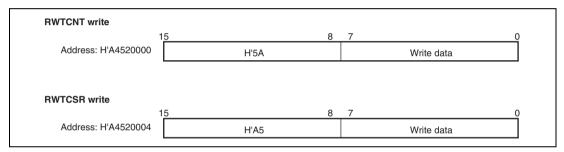

| 19.3  | _       | r Descriptions for RWDT                              |       |

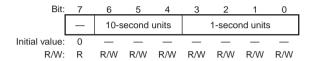

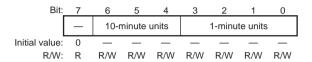

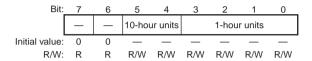

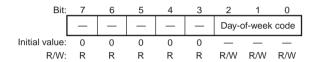

|       | _       | RCLK Watchdog Timer Counter (RWTCNT)                 |       |

|       |         | RCLK Watchdog Timer Control/Status Register (RWTCSR) |       |

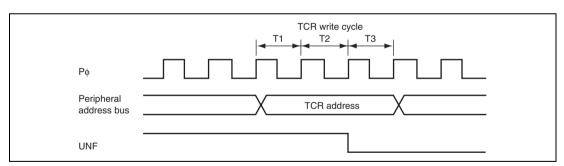

|       |         | Notes on Register Access                     |     |

|-------|---------|----------------------------------------------|-----|

| 19.4  | RWDT    | 'Usage                                       | 594 |

|       | 19.4.1  | Control of System Runaway                    | 594 |

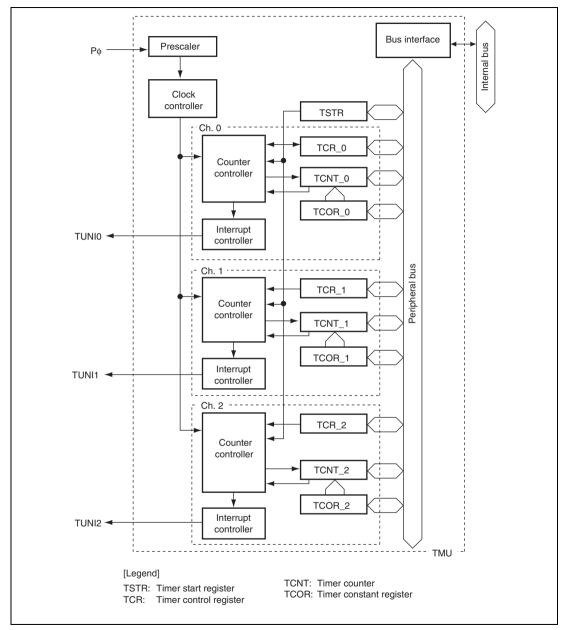

| Secti | ion 20  | Timer Unit (TMU)                             | 595 |

| 20.1  |         | 28                                           |     |

| 20.2  |         | er Descriptions                              |     |

|       | 20.2.1  | Timer Start Register 0,1 (TSTR0, TSTR1)      | 599 |

|       | 20.2.2  | Timer Control Registers 0, 1 (TCR0, TCR1)    |     |

|       |         | Timer Constant Registers 0, 1 (TCOR0, TCOR1) |     |

|       | 20.2.4  | Timer Counters 0, 1 (TCNT0, TCNT 1)          | 602 |

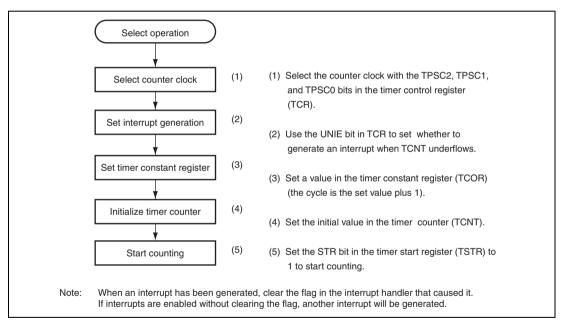

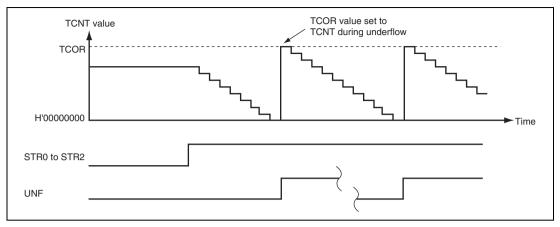

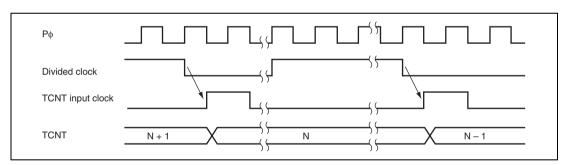

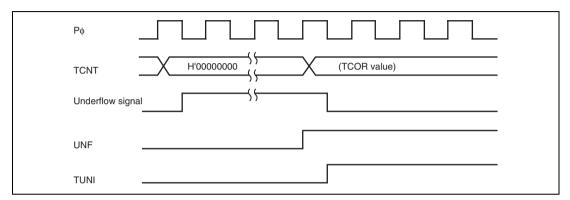

| 20.3  | Operati | ion                                          | 603 |

|       | 20.3.1  | Counter Operation.                           | 603 |

| 20.4  | Interru | pts                                          | 605 |

|       | 20.4.1  | •                                            |     |

|       | 20.4.2  |                                              |     |

|       | 20.4.3  | Interrupt Sources and Priorities.            |     |

| 20.5  |         | Notes                                        |     |

|       | _       | Writing to Registers                         |     |

|       |         | Reading Registers                            |     |

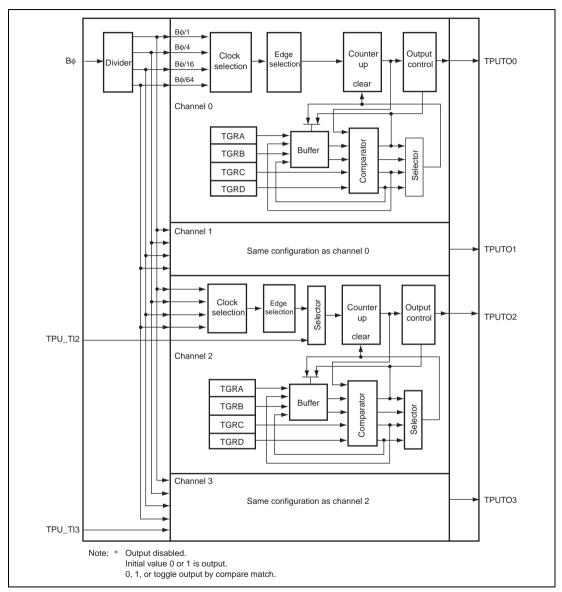

| Secti | ion 21  | 16-Bit Timer Pulse Unit (TPU)                | 607 |

| 21.1  |         | es                                           |     |

| 21.2  |         | Diagram                                      |     |

| 21.3  |         | Output Pin                                   |     |

| 21.4  | -       | er Descriptions                              |     |

|       | 21.4.1  | Timer Control Register (TPU_TCR)             |     |

|       | 21.4.2  | Timer Mode Register (TPU_TMDR)               |     |

|       | 21.4.3  | Timer I/O Control Register (TPU_TIOR)        |     |

|       | 21.4.4  | Timer Interrupt Enable Register (TPU_TIER)   |     |

|       | 21.4.5  | Timer Status Registers (TPU_TSR)             |     |

|       | 21.4.6  | Timer Counter (TPU_TCNT)                     |     |

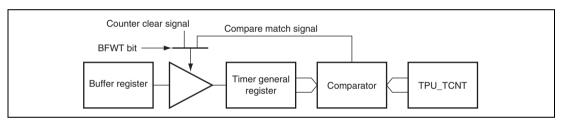

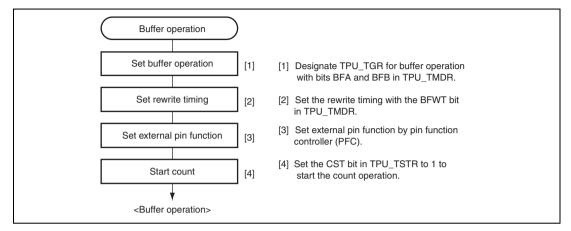

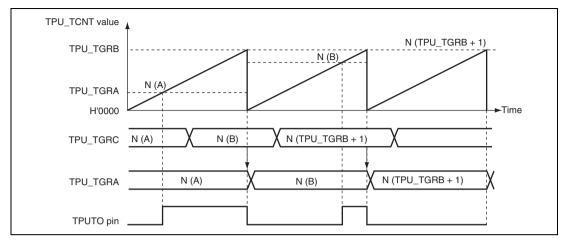

|       | 21.4.7  | Timer General Register (TPU_TGR)             |     |

|       | 21.4.8  | Timer Start Register (TPU_TSTR)              |     |

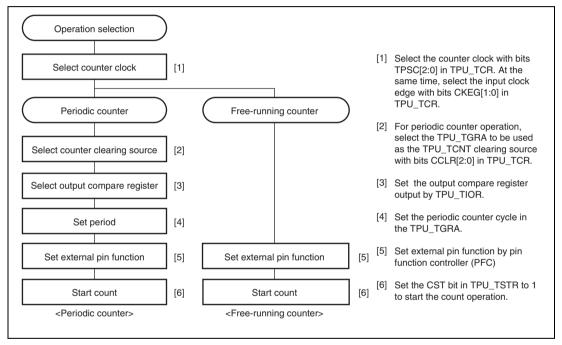

| 21.5  |         | ion                                          |     |

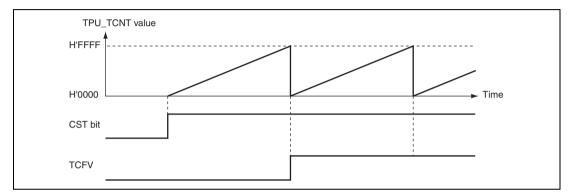

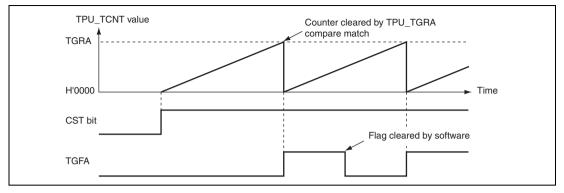

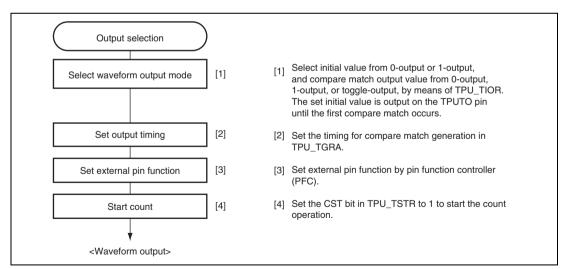

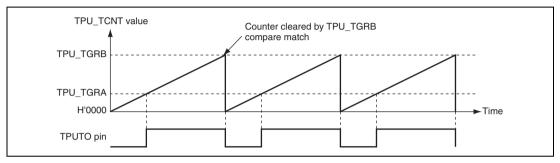

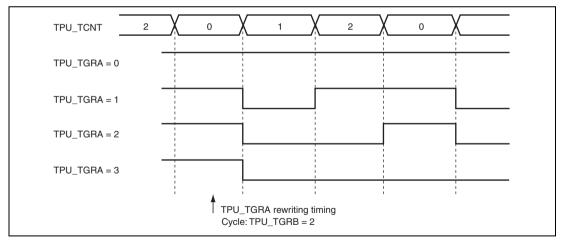

|       | 21.5.1  |                                              |     |

|       | 21.5.2  | Basic Functions                              |     |

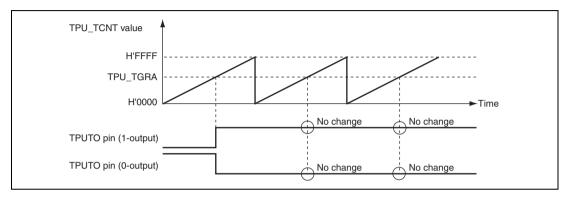

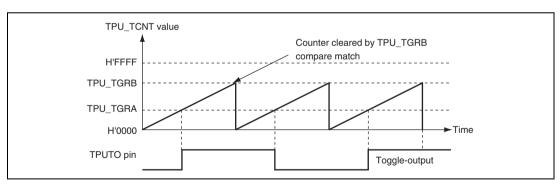

|       | 21.5.3  |                                              |     |

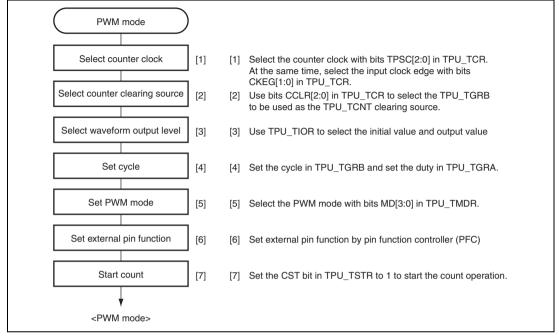

|       |         | PWM Modes                                    |     |

|       |         |                                              |     |

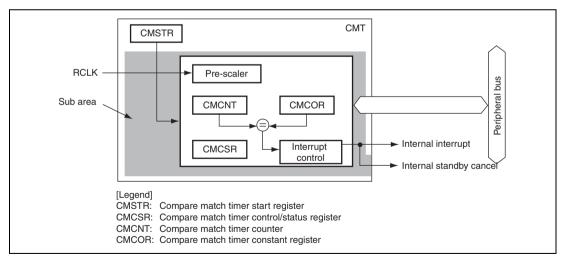

| Secti | ion 22            | Compare Match Timer (CMT)                                        | 633 |

|-------|-------------------|------------------------------------------------------------------|-----|

| 22.1  | Feature           | 28                                                               | 633 |

| 22.2  | Registe           | er Descriptions                                                  | 634 |

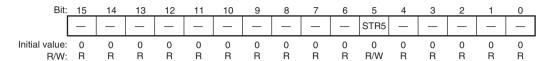

|       | 22.2.1            | Compare Match Timer Start Register (CMSTR)                       | 635 |

|       | 22.2.2            | Compare Match Timer Control/Status Register (CMCSR)              | 636 |

|       | 22.2.3            | Compare Match Timer Counter (CMCNT)                              | 639 |

|       | 22.2.4            | Compare Match Timer Constant Register (CMCOR)                    | 639 |

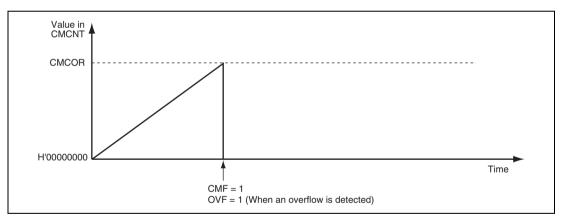

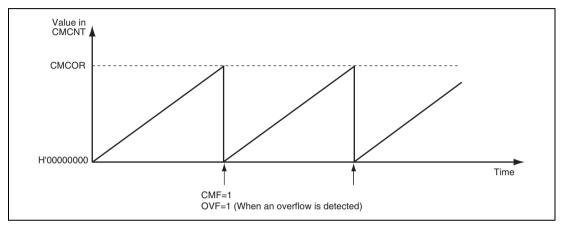

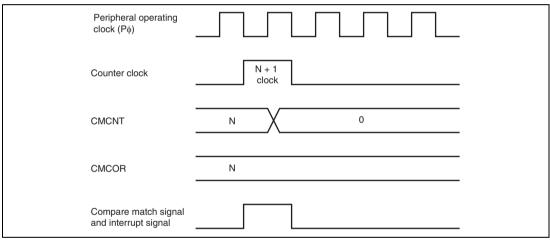

| 22.3  | Operat            | ion                                                              | 640 |

|       | 22.3.1            | Counter Operation                                                | 640 |

|       | 22.3.2            | Counter Size                                                     | 641 |

|       | 22.3.3            | Timing for Counting by CMCNT                                     | 641 |

|       | 22.3.4            | Internal Interrupt Request to CPU                                | 642 |

|       | 22.3.5            | CMT Operation                                                    | 642 |

|       | 22.3.6            | Compare Match Flag Set Timing                                    | 643 |

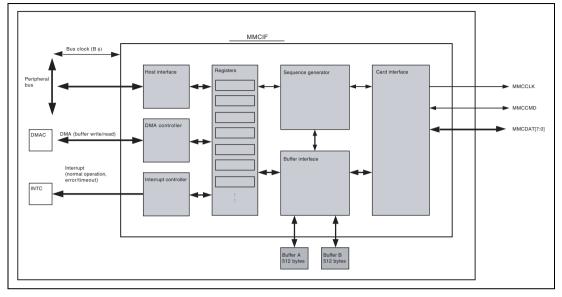

| Secti | ion 23            | Multi Media Card Interface (MMCIF)                               | 645 |

| 23.1  | Feature           | es                                                               | 645 |

| 23.2  | Input/Output Pins |                                                                  |     |

| 23.3  | Registe           | er Descriptions                                                  | 647 |

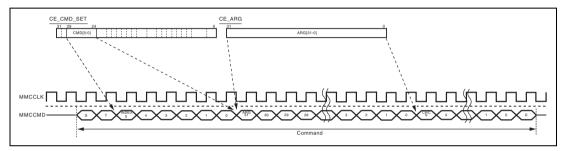

|       | 23.3.1            | Command Setting Register (CE_CMD_SET)                            | 649 |

|       |                   | Argument Register (CE_ARG)                                       |     |

|       | 23.3.3            | Argument Register for Automatically-Issued CMD12 (CE_ARG_CMD12)  | 652 |

|       |                   | Command Control Register (CE_CMD_CTRL)                           |     |

|       |                   | Transfer Block Setting Register (CE_BLOCK_SET)                   |     |

|       |                   | Clock Control Register (CE_CLK_CTRL)                             |     |

|       |                   | Buffer Access Configuration Register (CE_BUF_ACC)                |     |

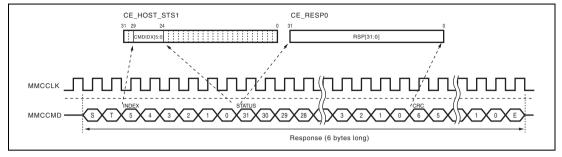

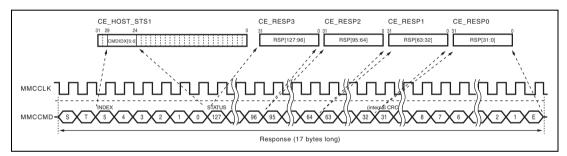

|       |                   | Response Registers 3 to 0 (CE_RESP3 to CE_RESP0)                 |     |

|       | 23.3.9            | Response Register for Automatically-Issued CMD12 (CE_RESP_CMD12) | 660 |

|       |                   | Data Register (CE_DATA)                                          |     |

|       | 23.3.11           | Interrupt Flag Register (CE_INT)                                 | 661 |

|       |                   | 2 Interrupt Mask Register (CE_INT_MASK)                          |     |

|       |                   | B Status Register 1 (CE_HOST _STS1)                              |     |

|       |                   | Status Register 2 (CE_HOST _STS2)                                |     |

|       |                   | 5 Version Register (CE_VERSION)                                  |     |

| 23.4  | Interru           | pt Requests                                                      | 676 |

| 23.5  |                   | Specifications                                                   |     |

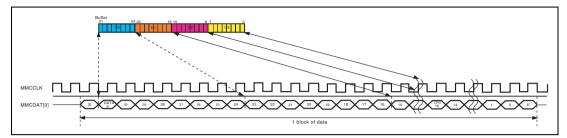

|       |                   | DMA for Buffer Writing                                           |     |

|       | 23.5.2            | DMA for Buffer Reading                                           | 677 |

| 23.6  | Operat            | ion                                                              | 678 |

|       | 23.6.1            | Command/Response Formats                                         | 678 |

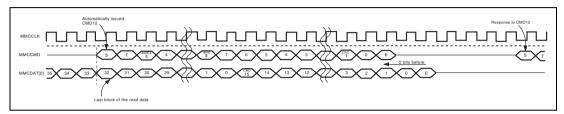

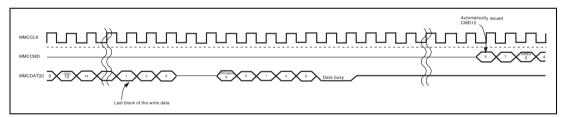

|      | 23.6.2                                                 | Automatic CMD12 Issuance                                       | 680 |

|------|--------------------------------------------------------|----------------------------------------------------------------|-----|

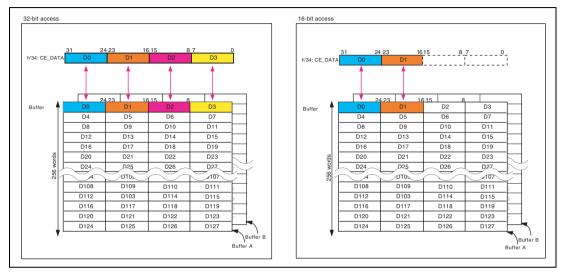

|      | 23.6.3                                                 | Buffer Structure                                               | 681 |

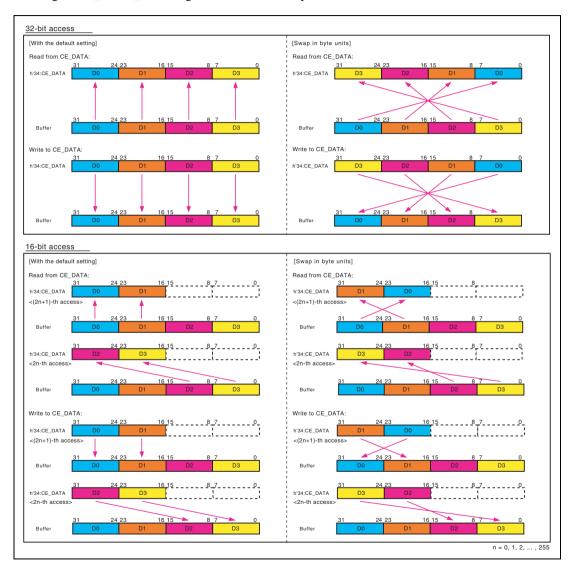

|      | 23.6.4                                                 | Buffer Access Select Function in Access to CE_DATA             | 682 |

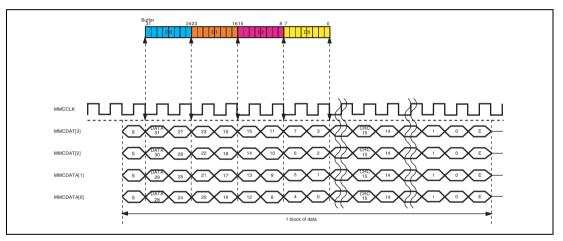

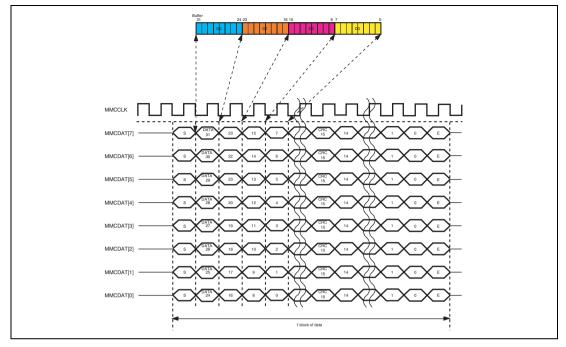

|      |                                                        | Data Formats                                                   |     |

|      |                                                        | Operation in the Case of Error/Timeout                         |     |

| 23.7 |                                                        | les of Setting                                                 |     |

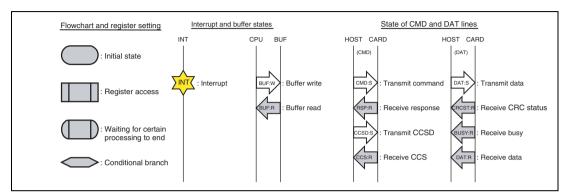

|      | -                                                      | Legends                                                        |     |

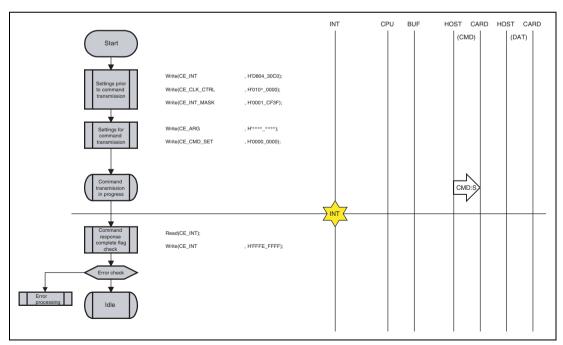

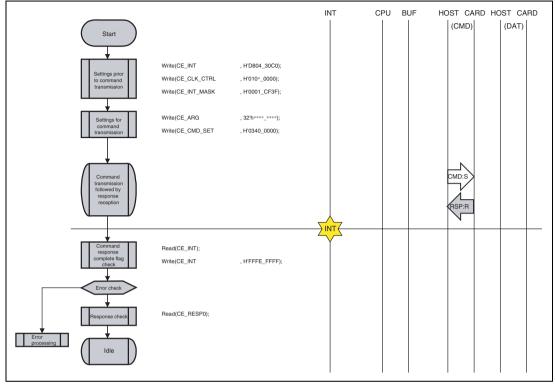

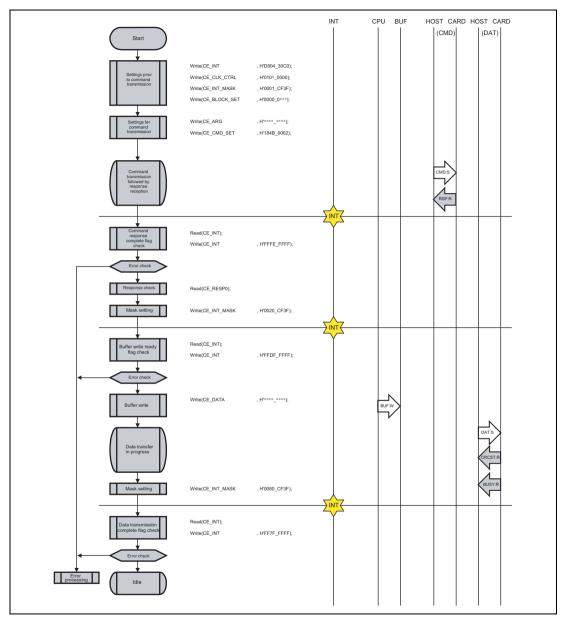

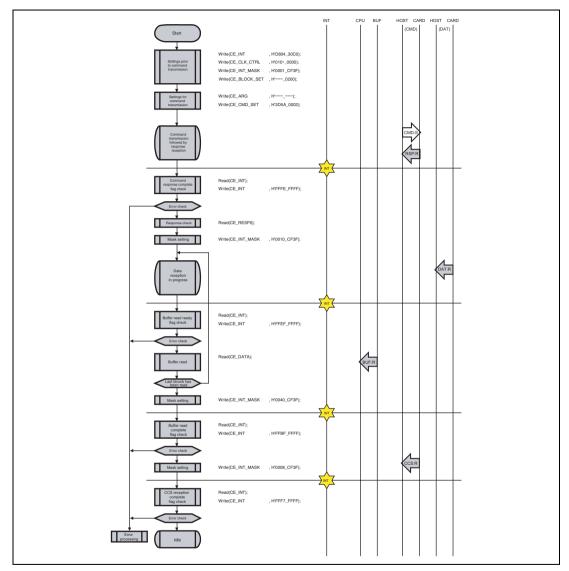

|      | 23.7.2                                                 | Command Transmission                                           | 685 |

|      |                                                        | Command Transmission → Response Reception                      |     |

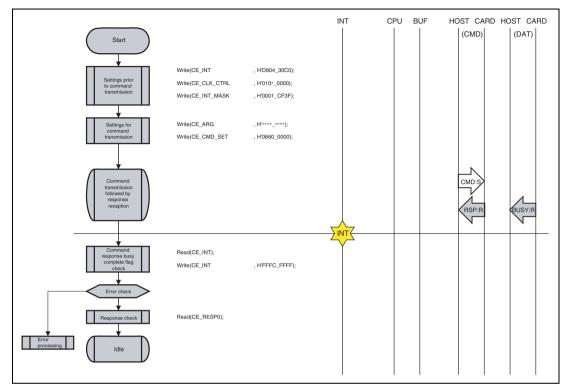

|      | 23.7.4                                                 | Command Transmission → Response Reception (with Response Busy) | 687 |

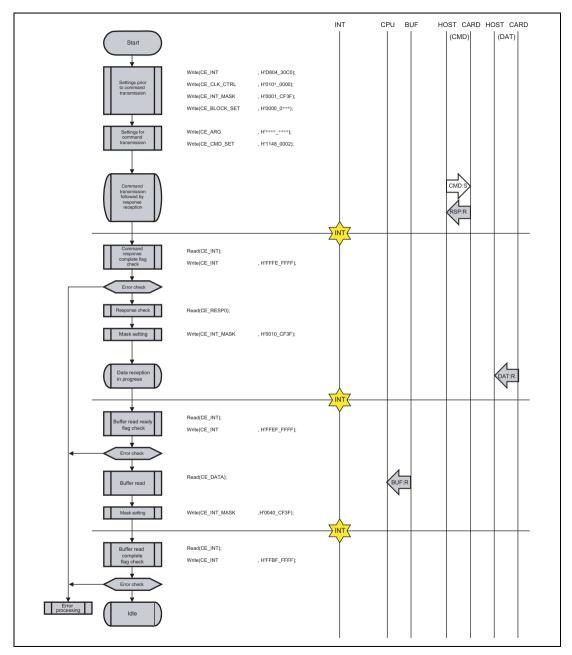

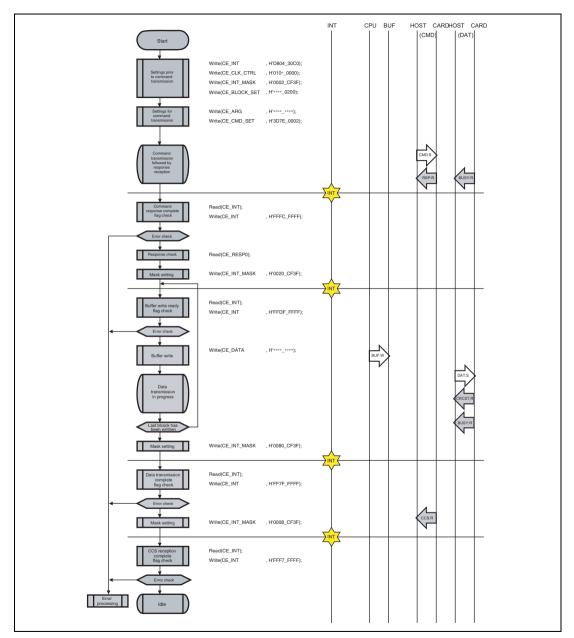

|      | 23.7.5                                                 |                                                                |     |

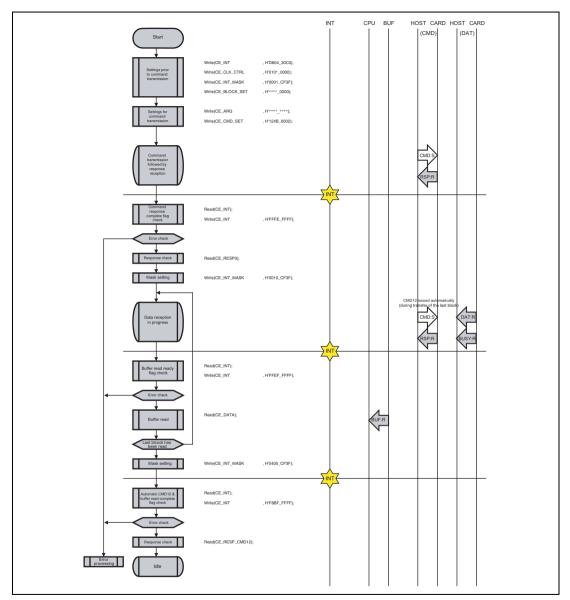

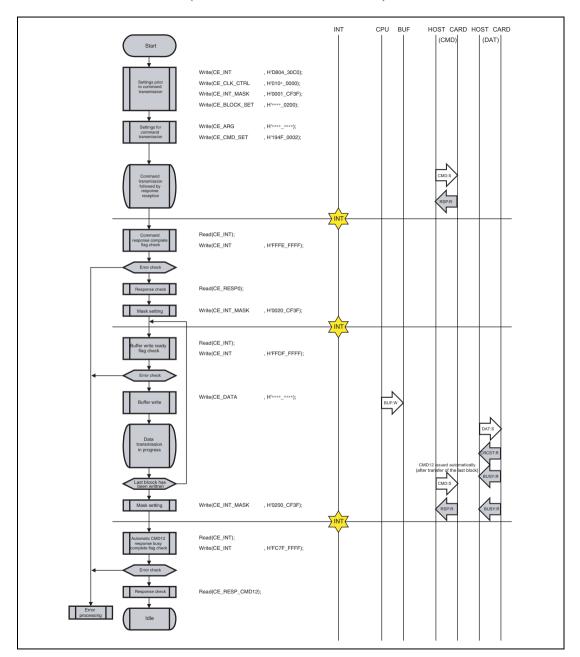

|      | 23.7.6                                                 | Multi-Block Read (with Automatic CMD12 Issuance)               |     |

|      | 23.7.7                                                 | Single-Block Write                                             | 690 |

|      | 23.7.8                                                 | Multi-Block Write (with Automatic CMD12 Issuance)              |     |

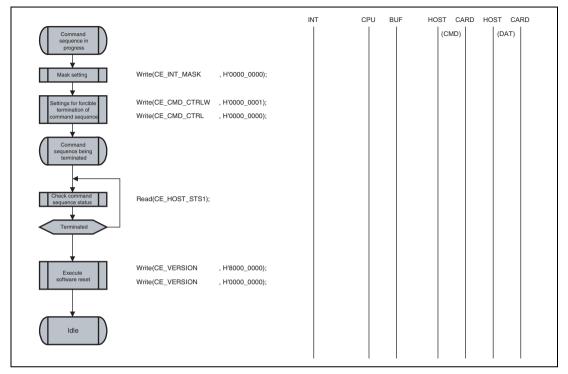

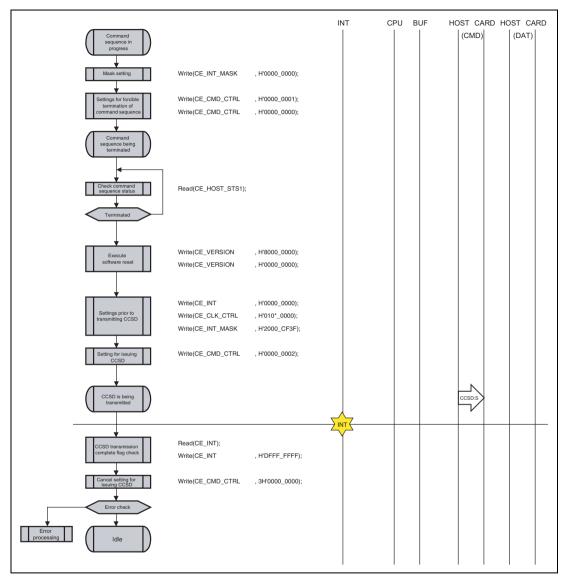

|      | 23.7.9                                                 | Forcible Termination                                           | 692 |

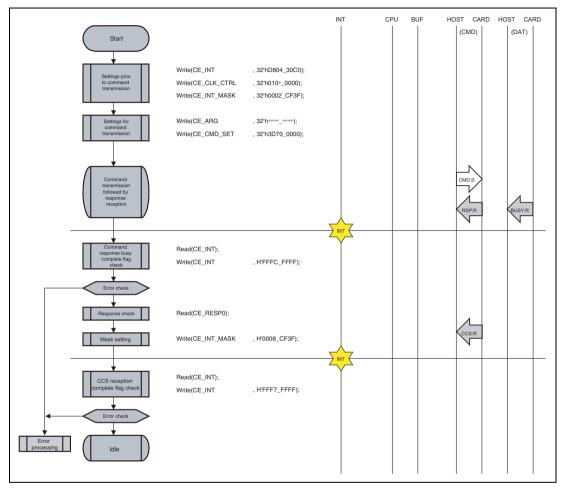

|      | 23.7.10                                                | ) Command Transmission → Response Reception                    |     |

|      |                                                        | (with Response Busy and CCS)                                   | 693 |

|      | 23.7.1                                                 | Multi-Block Read (with CCS)                                    | 694 |

|      | 23.7.12 Multi-Block Write (with Response Busy and CCS) |                                                                |     |

|      |                                                        | 3 Forcible Termination → Transmission of CCSD                  |     |

|      | 23.7.14                                                | 4 Setting Values of CE_CMD_SET                                 | 697 |

| 23.8 | Usage                                                  | Notes                                                          | 699 |

|      | 23.8.1                                                 | Forcible Termination                                           | 699 |

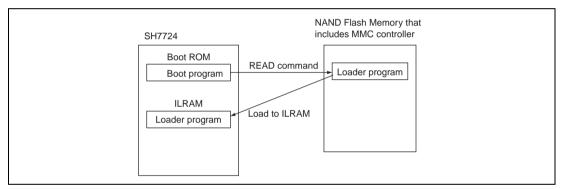

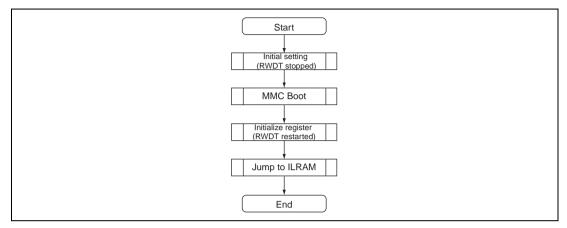

| Sect | ion 24                                                 | Flash Memory Boot ROM (FBR)                                    | 701 |

| 24.1 |                                                        | es                                                             |     |

| 24.2 |                                                        | Output Pins                                                    |     |

| 24.3 | -                                                      | ew of Boot Program                                             |     |

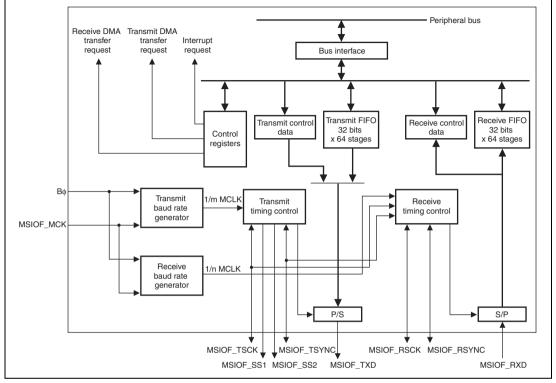

| Sect | ion 25                                                 | Clock-Synchronized Serial Interface with FIFO (MSIOF)          | 705 |

| 25.1 |                                                        | es                                                             |     |

| 25.2 |                                                        | Output Pins                                                    |     |

| 25.3 |                                                        | er Descriptions                                                |     |

|      | _                                                      | MSIOF Transmit Mode Register 1                                 |     |

|      |                                                        | (MSIOF 0_SITMDR1, MSIOF 1_SITMDR1)                             | 711 |

|      | 25.3.2                                                 |                                                                |     |

|      |                                                        | (MSIOFO_SITMDR2, MSIOF1_SITMDR2)                               | 716 |

|      | 25.3.3                                                 | MSIOF Transmit Mode Register 3                                 |     |

|      |                                                        | (MSIOF0_SITMDR3, MSIOF1_SITMDR3,)                              | 718 |

|      |                                                        |                                                                |     |

|       | 25.3.4  | MSIOF Receive Mode Register 1                                   |       |

|-------|---------|-----------------------------------------------------------------|-------|

|       |         | (MSIOF0_SIRMDR1, MSIOF1_SIRMDR1)                                | . 719 |

|       | 25.3.5  | MSIOF Receive Mode Register 2                                   |       |

|       |         | (MSIOF0_SIRMDR2, MSIOF1_SIRMDR2)                                | . 724 |

|       | 25.3.6  | MSIOF Receive Mode Register 3                                   |       |

|       |         | (MSIOF0_SIRMDR3, MSIOF1_SIRMDR3)                                | . 726 |

|       | 25.3.7  | MSIOF Control Register (MSIOF0_SICTR, MSIOF1_SICTR)             | . 728 |

|       | 25.3.8  | MSIOF Transmit Clock Select Register                            |       |

|       |         | (MSIOF0_SITSCR, MSIOF1_SITSCR)                                  | . 735 |

|       | 25.3.9  | MSIOF Receive Clock Select Register                             |       |

|       |         | (MSIOF0_SIRSCR, MSIOF1_SIRSCR)                                  | . 737 |

|       | 25.3.10 | MSIOF Transmit Control Data Register 1                          |       |

|       |         | (MSIOF0_SITDR1, MSIOF1_STDR1)                                   | . 739 |

|       | 25.3.11 | MSIOF Transmit Control Data Register 2                          |       |

|       |         | (MSIOF0_SITDR2, MSIOF1_SITDR2)                                  | . 740 |

|       | 25.3.12 | MSIOF Transmit FIFO Data Register                               |       |

|       |         | (MSIOF0_SITFDR, MSIOF1_SITFDR)                                  | . 741 |

|       | 25.3.13 | MSIOF Receive Control Data Register 1                           |       |

|       |         | (MSIOF0_SIRDR1, MSIOF1_SIRDR1)                                  | . 742 |

|       | 25.3.14 | MSIOF Receive Control Data Register 2                           |       |

|       |         | (MSIOF0_SIRDR2, MSIOF1_SIRDR2)                                  | . 743 |

|       | 25.3.15 | MSIOF Receive FIFO Data Register (MSIOF0_SIRFDR, MSIOF1_SIRFDR) | . 744 |

|       | 25.3.16 | MSIOF Status Register (MSIOF0_SISTR, MSIOF1_SISTR)              | . 745 |

|       | 25.3.17 | MSIOF Interrupt Enable Register (MSIOF0_SIIER, MSIOF1_SIIER)    | . 752 |

|       | 25.3.18 | MSIOF FIFO Control Register (MSIOF0_SIFCTR, MSIOF1_SIFCTR)      | . 755 |

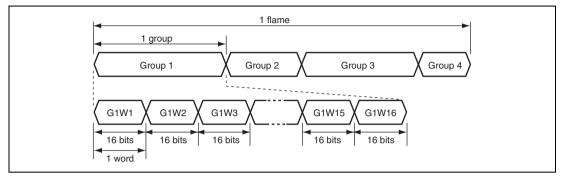

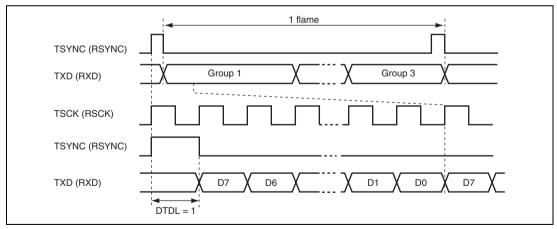

| 25.4  | Operati | on                                                              | . 757 |

|       | 25.4.1  | Operating Mode                                                  | . 757 |

|       | 25.4.2  | Serial Clocks                                                   | . 757 |

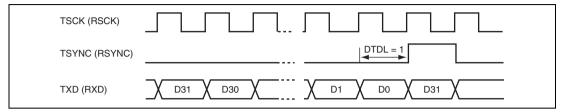

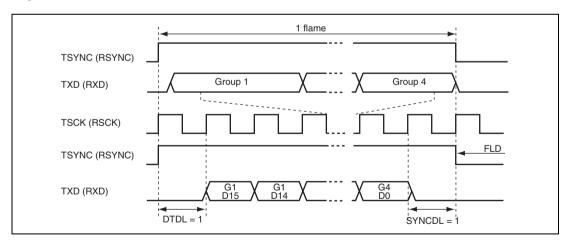

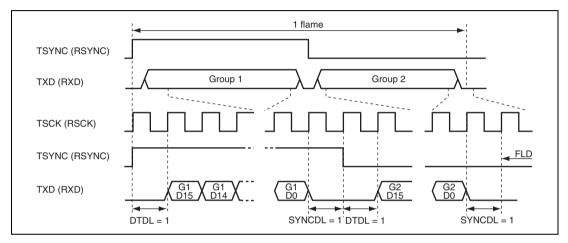

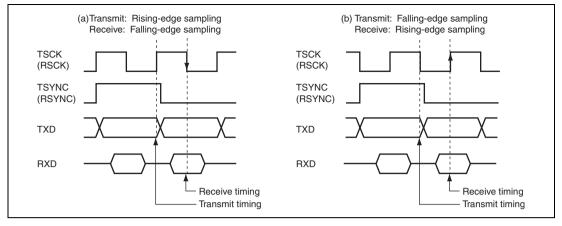

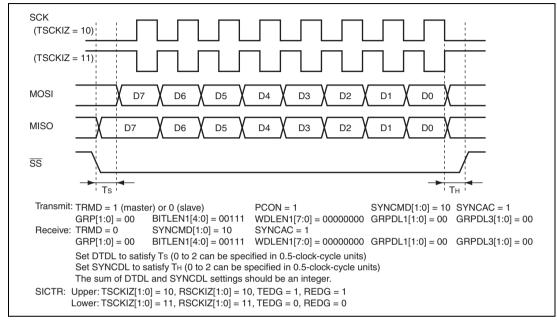

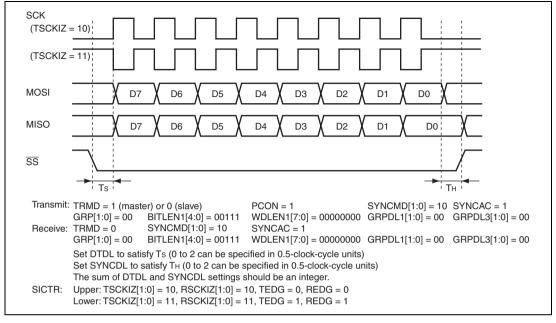

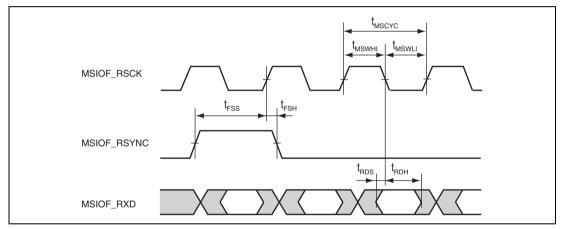

|       | 25.4.3  | Serial Timing                                                   | . 759 |

|       | 25.4.4  | Control Data Interface                                          | . 762 |

|       | 25.4.5  | Transfer Data Allocation to Registers                           | . 763 |

|       | 25.4.6  | FIFO                                                            | . 764 |

|       | 25.4.7  | Transmit and Receive Procedures                                 | . 766 |

|       | 25.4.8  | Interrupts                                                      | . 771 |

|       | 25.4.9  | Transmit and Receive Timing                                     | . 773 |

|       |         | SPI                                                             |       |

|       | 25.4.11 | Usage Notes for SPI Mode                                        | . 778 |

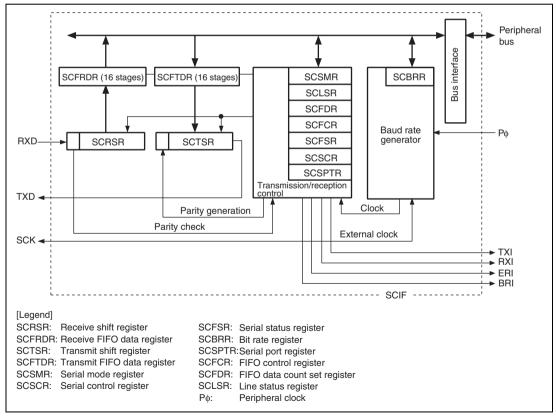

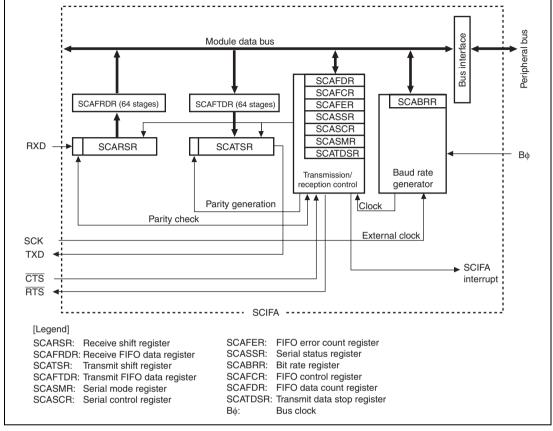

| Secti | on 26   | Serial Communication Interface with FIFO (SCIF)                 | 779   |

| 26.1  |         | S                                                               |       |

| 26.2  | Input/C | Output Pins                                                          | 781 |

|-------|---------|----------------------------------------------------------------------|-----|

| 26.3  | Registe | r Descriptions                                                       | 782 |

|       | 26.3.1  | Receive Shift Register (SCRSR)                                       | 784 |

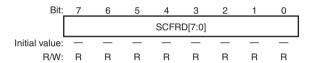

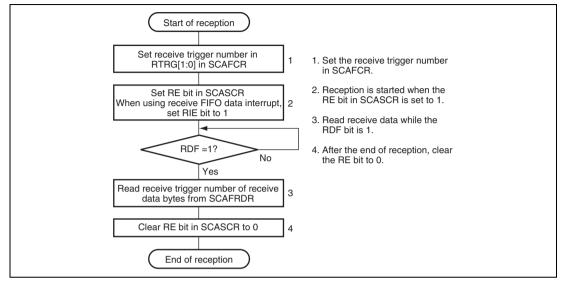

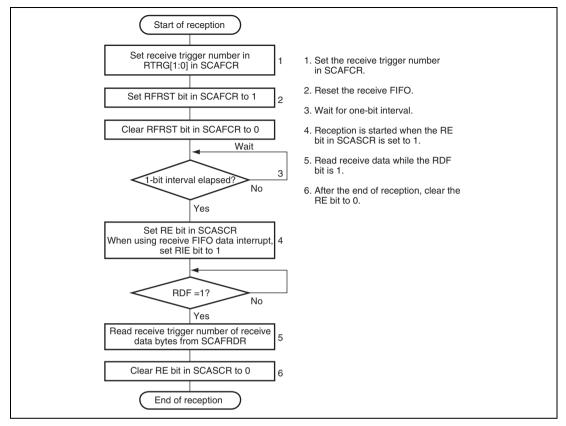

|       | 26.3.2  | Receive FIFO Data Register (SCFRDR)                                  | 784 |

|       | 26.3.3  | Transmit Shift Register (SCTSR)                                      | 785 |

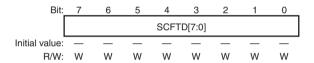

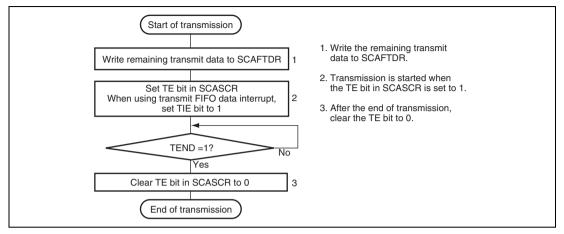

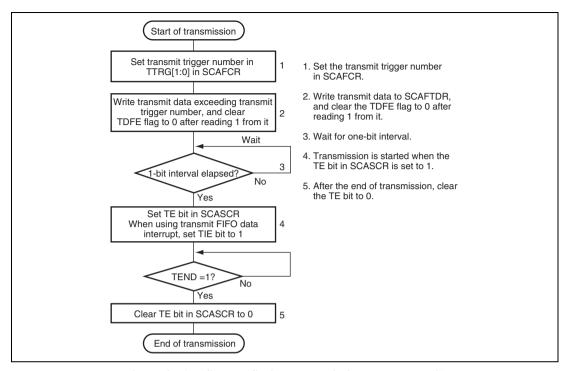

|       | 26.3.4  | Transmit FIFO Data Register (SCFTDR)                                 | 785 |

|       | 26.3.5  | Serial Mode Register (SCSMR)                                         | 786 |

|       | 26.3.6  | Serial Control Register (SCSCR)                                      | 789 |

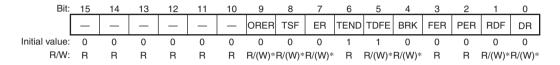

|       | 26.3.7  | Serial Status Register (SCFSR)                                       | 793 |

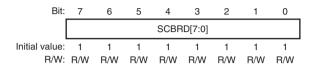

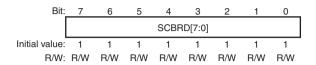

|       | 26.3.8  | Bit Rate Register (SCBRR)                                            | 799 |

|       | 26.3.9  | FIFO Control Register (SCFCR)                                        | 800 |

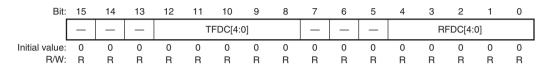

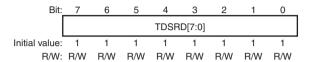

|       | 26.3.10 | FIFO Data Count Set Register (SCFDR)                                 | 802 |

|       | 26.3.11 | Line Status Register (SCLSR)                                         | 803 |

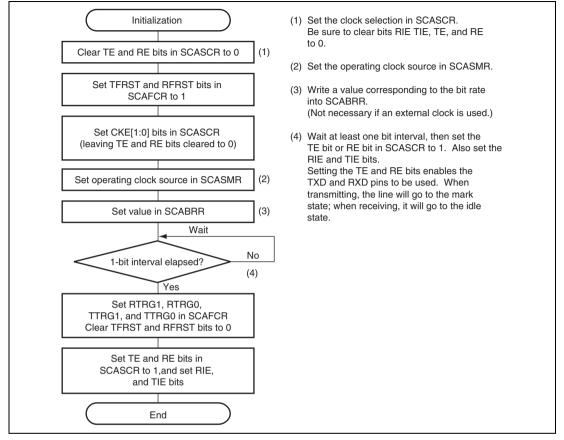

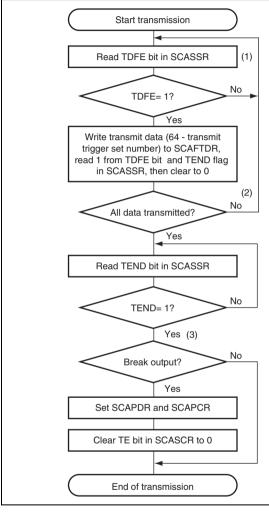

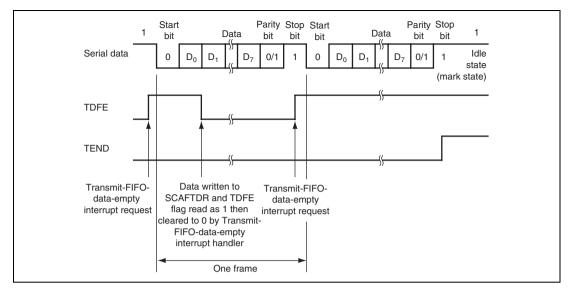

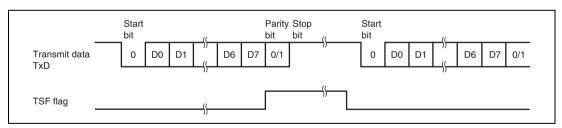

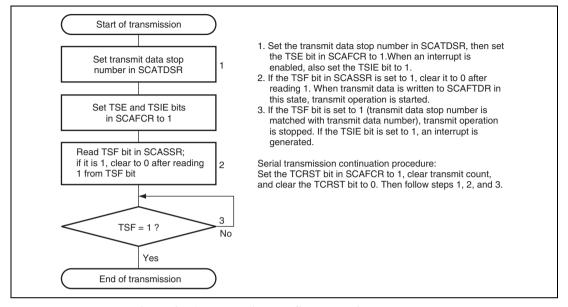

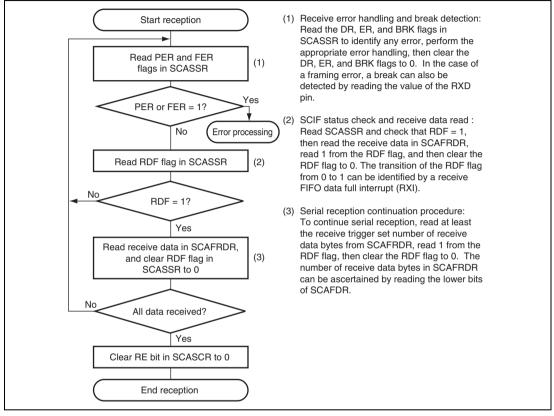

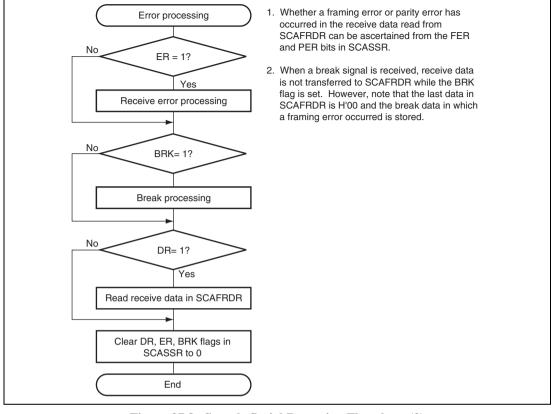

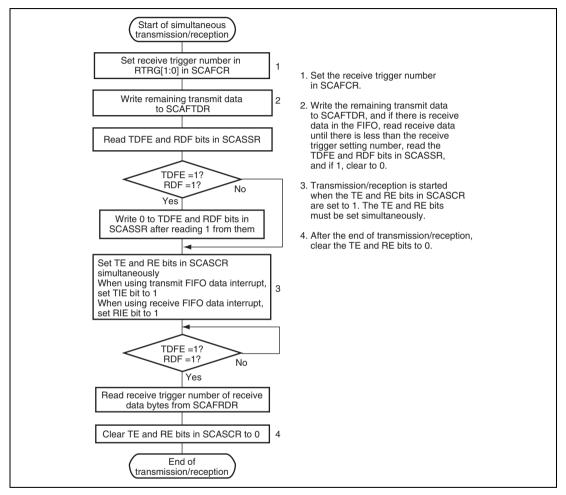

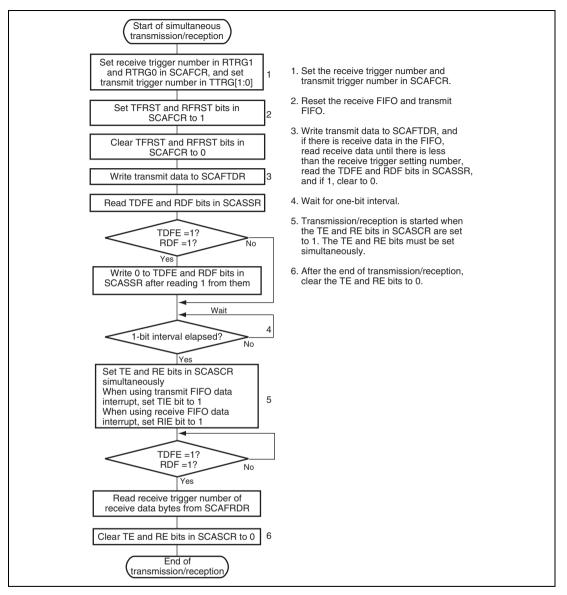

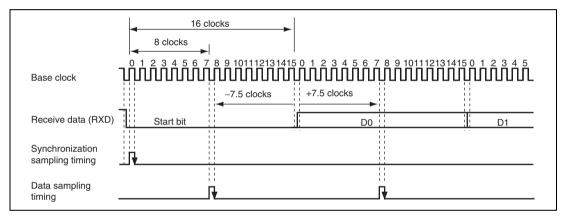

| 26.4  | Operati | on                                                                   | 804 |

|       | 26.4.1  | Overview                                                             | 804 |

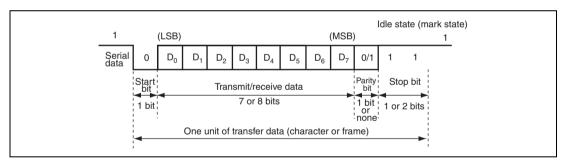

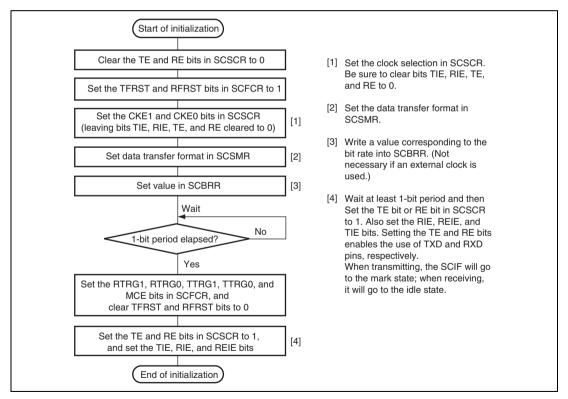

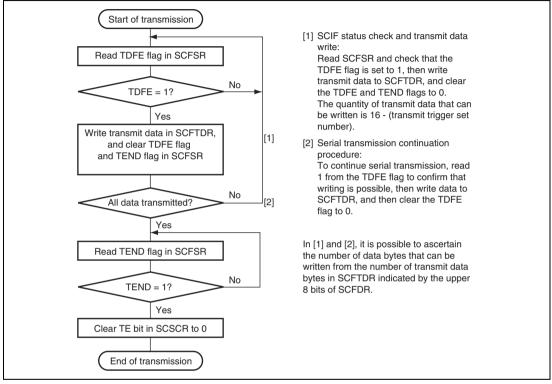

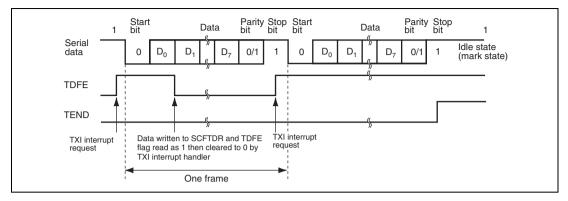

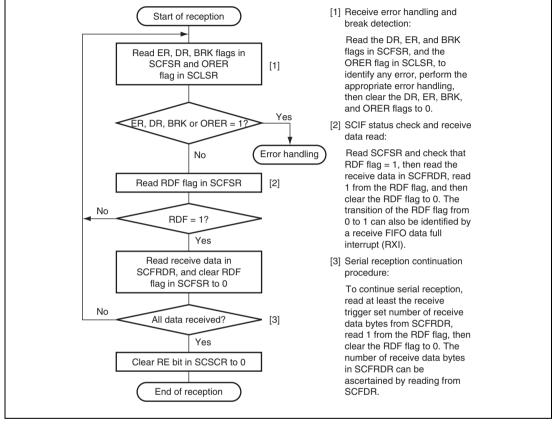

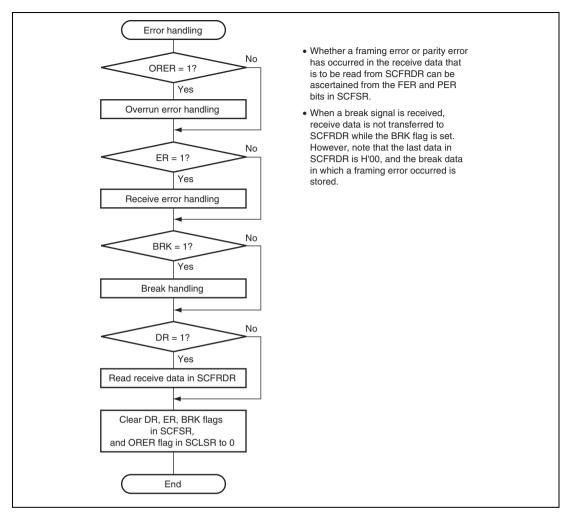

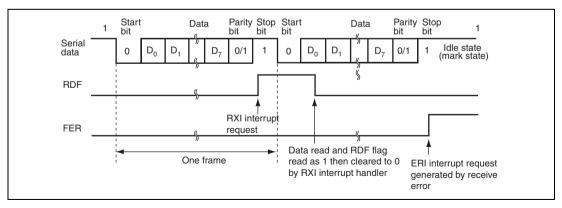

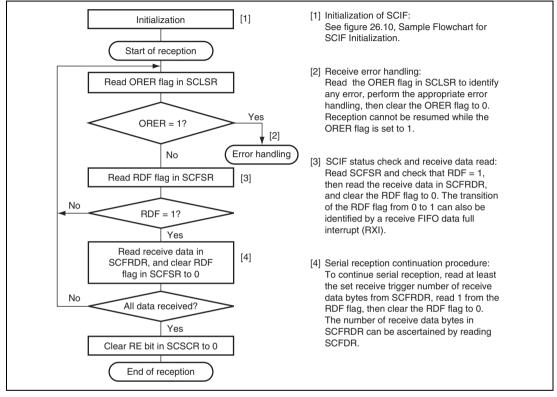

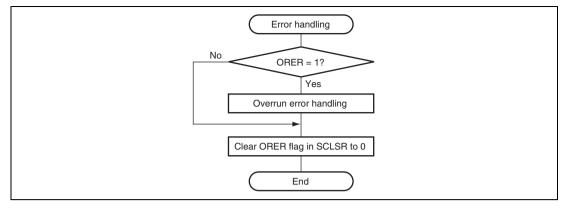

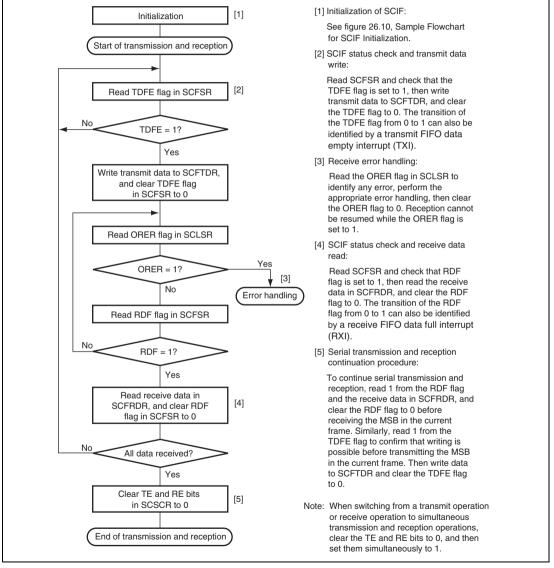

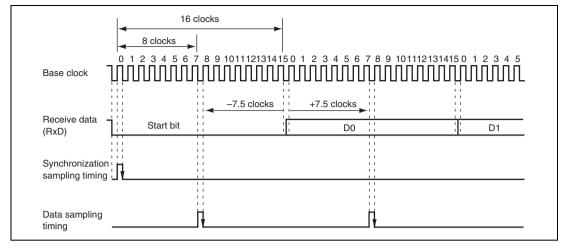

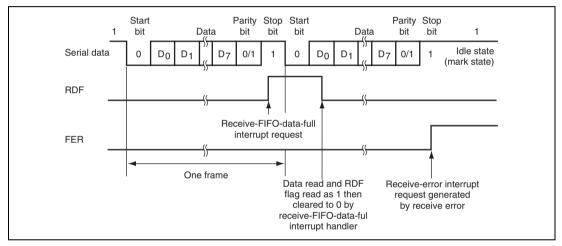

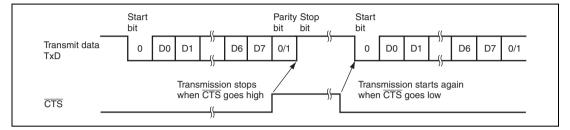

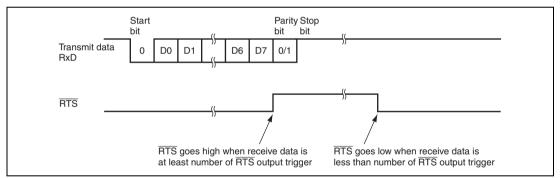

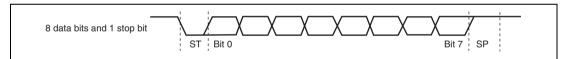

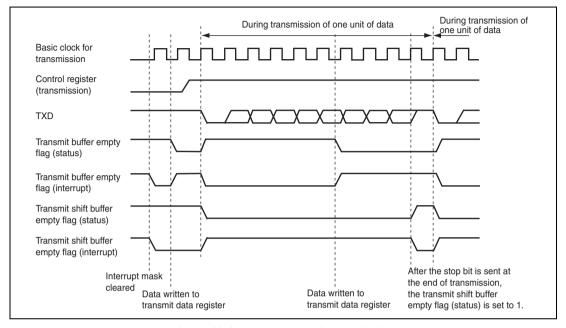

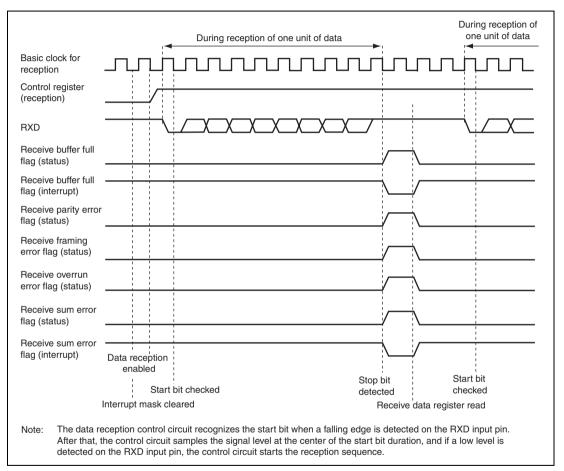

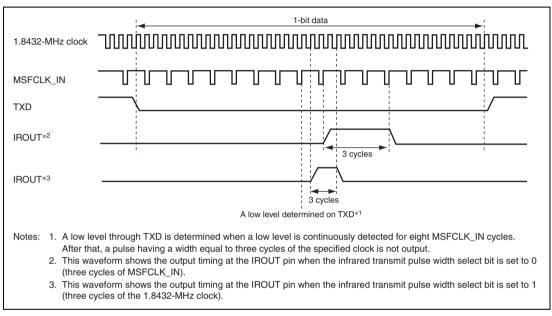

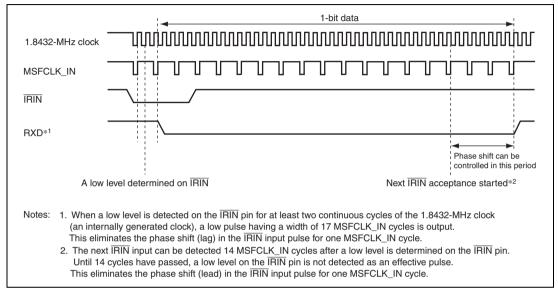

|       | 26.4.2  | Operation in Asynchronous Mode                                       | 806 |

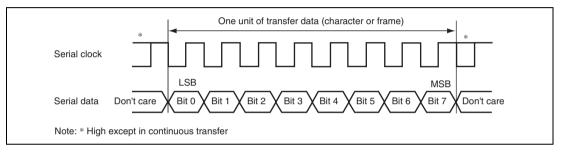

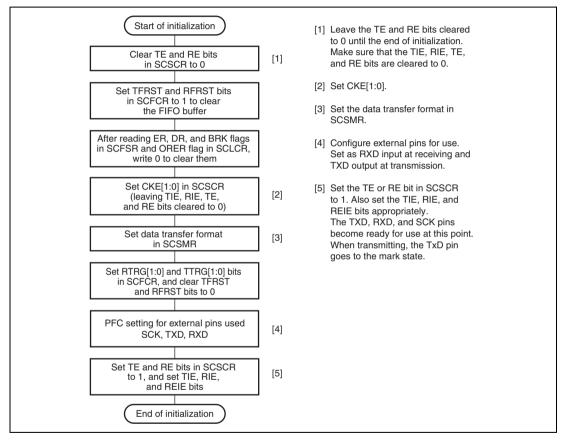

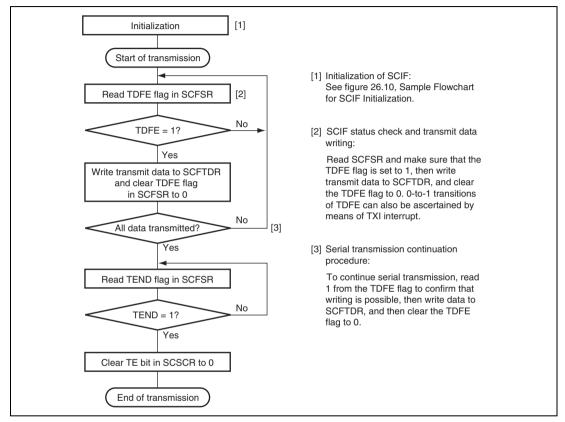

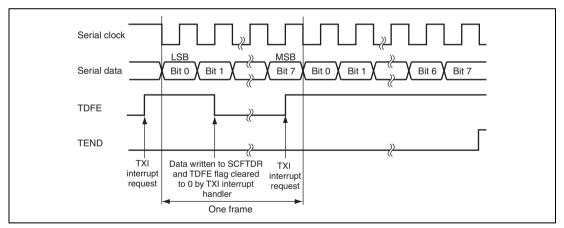

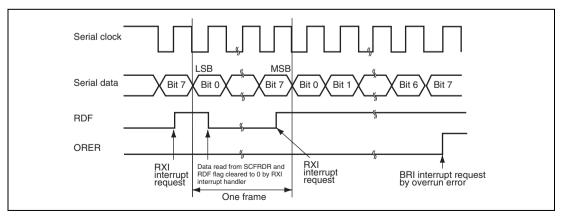

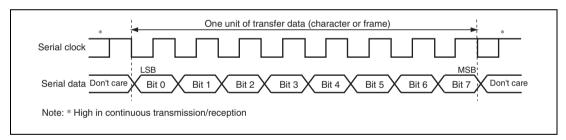

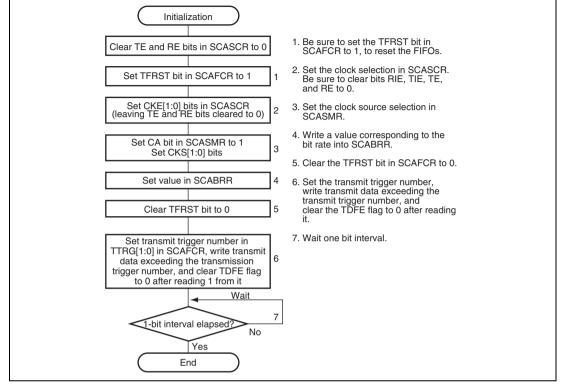

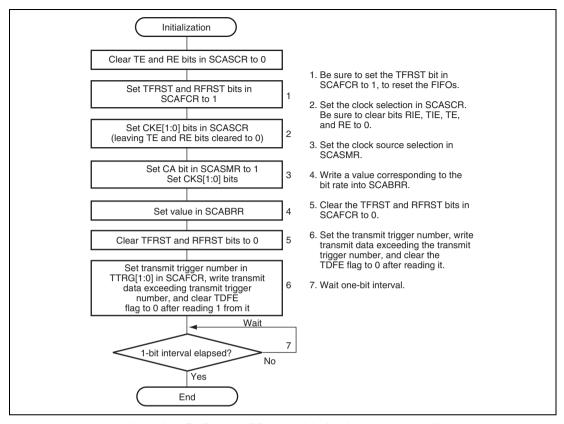

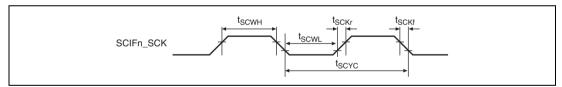

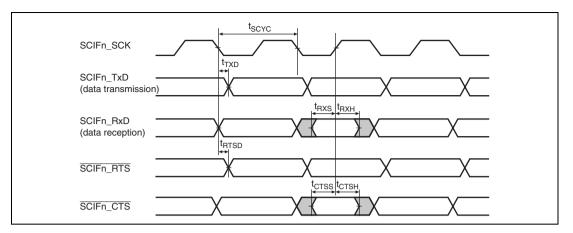

|       | 26.4.3  | Operation in Clock Synchronous Mode                                  | 815 |

| 26.5  | SCIF I  | nterrupt Sources and DMAC                                            | 822 |

| 26.6  | Usage 1 | Notes                                                                | 823 |